AMD預計在2024年7月底推出基於Zen 5架構的Granite Ridge「Ryzen 9000」桌上型處理器與Strix Point「Ryan AI 300」行動版處理器,在正式推出前夕,AMD又提供補充資料進一步介紹Zen 5架構、Strix Point「Ryan AI 300」與Granite Ridge「Ryzen 9000」的細節。

Zen 5架構進一步資訊細節

▲Zen 5設計概述,同樣提供Zen 5與Zen 5c兩種設計

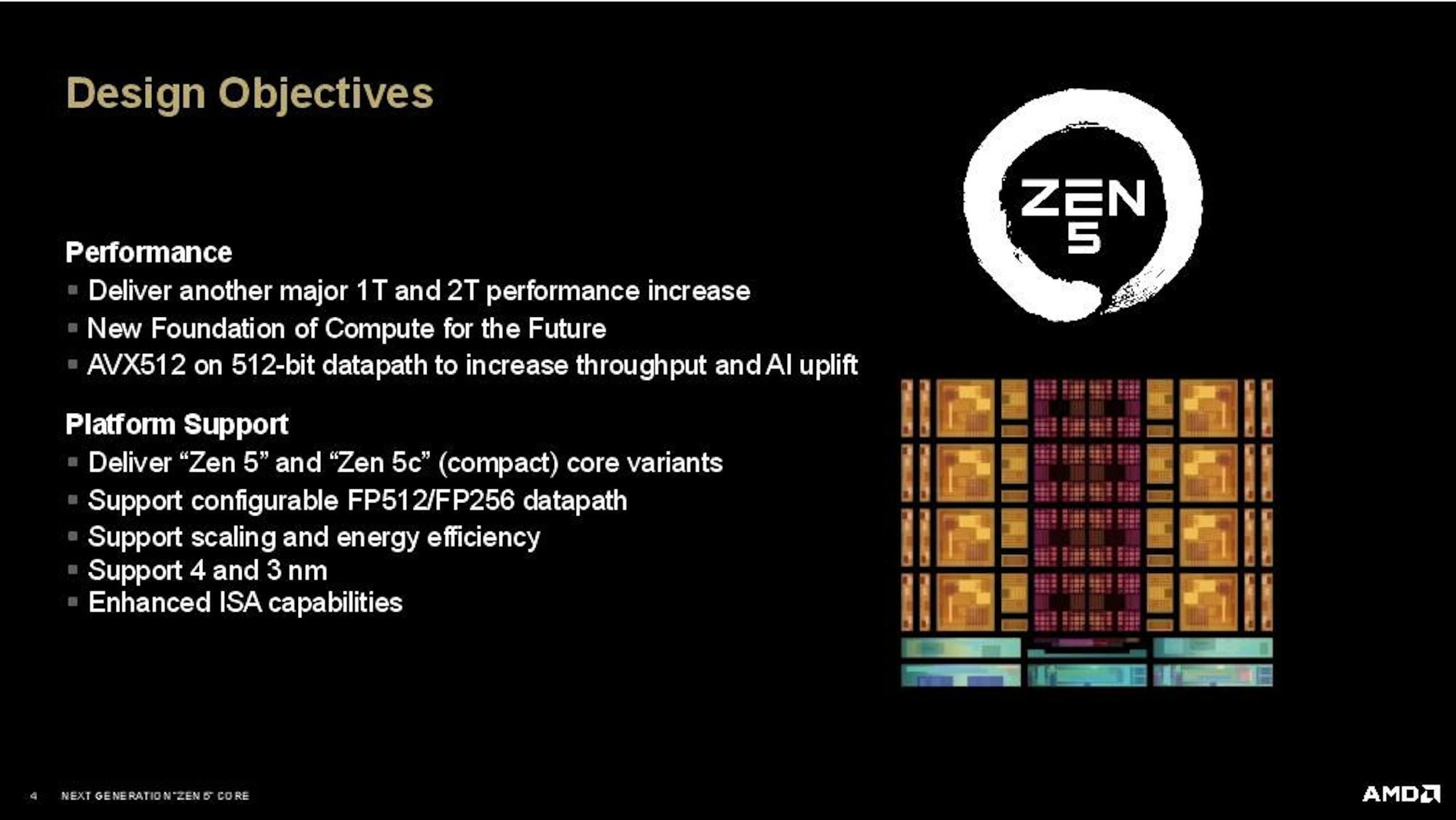

▲更出色的分支預測設計與結構

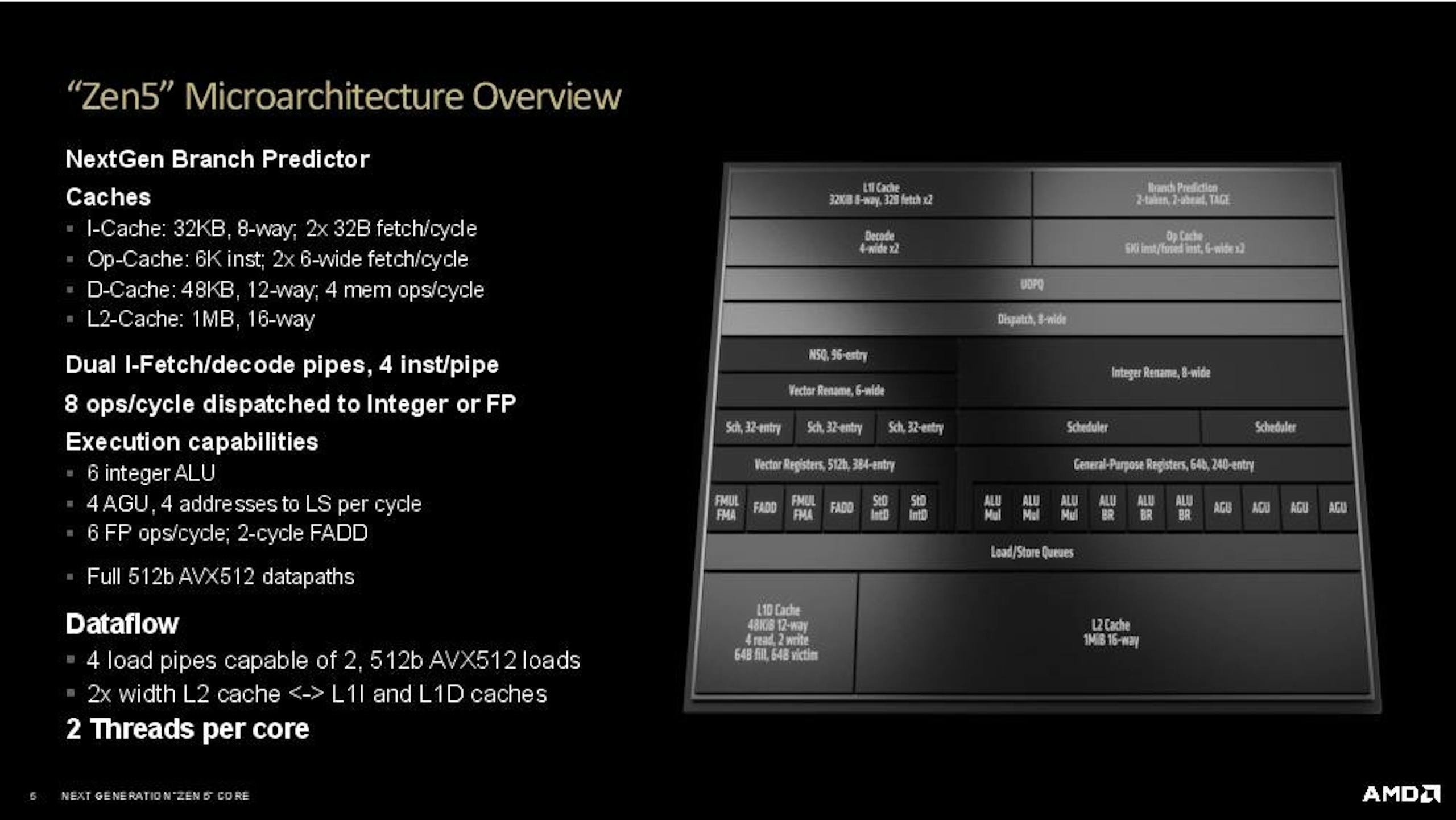

▲Zen 5與Zen 5c的差異

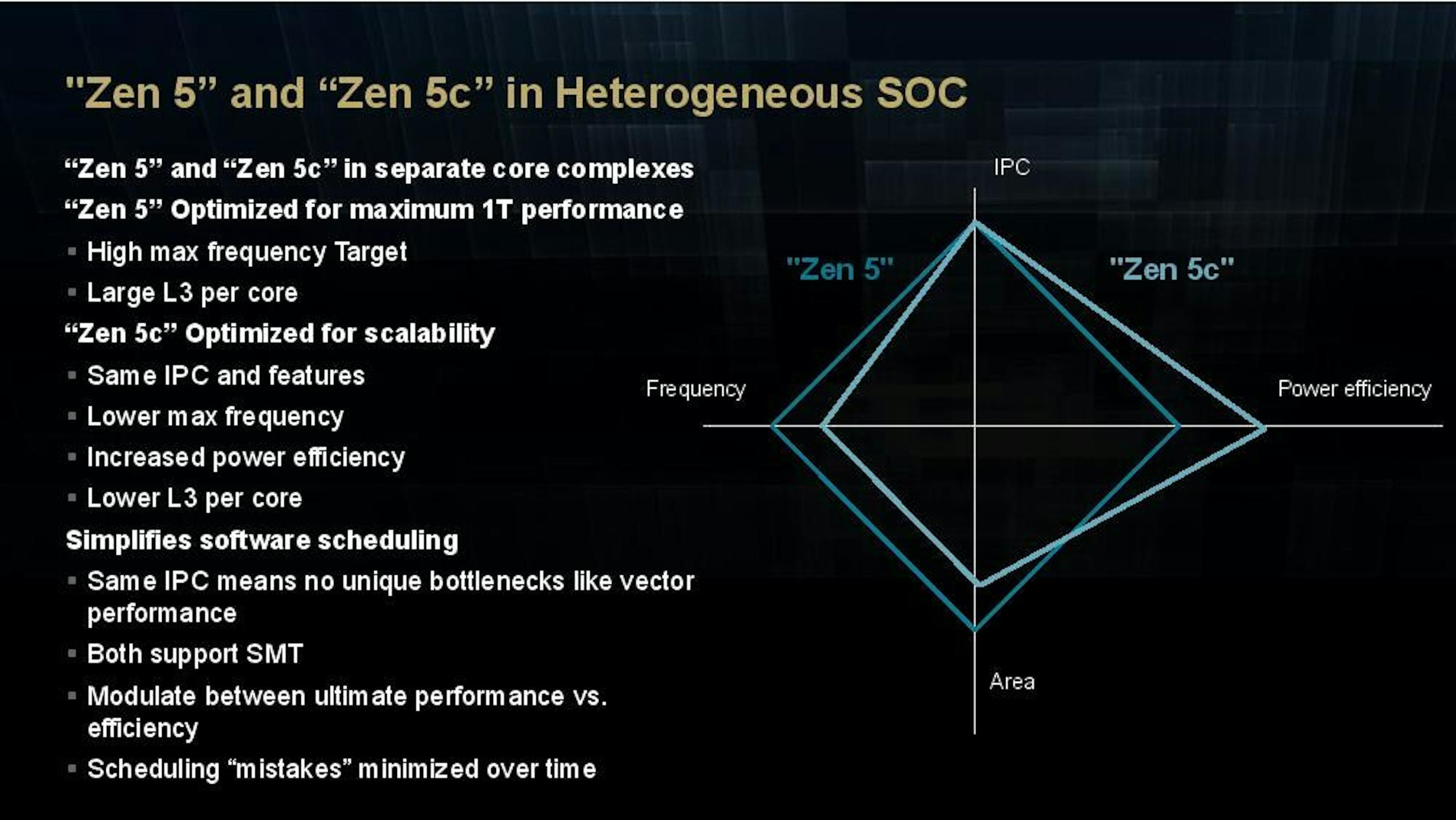

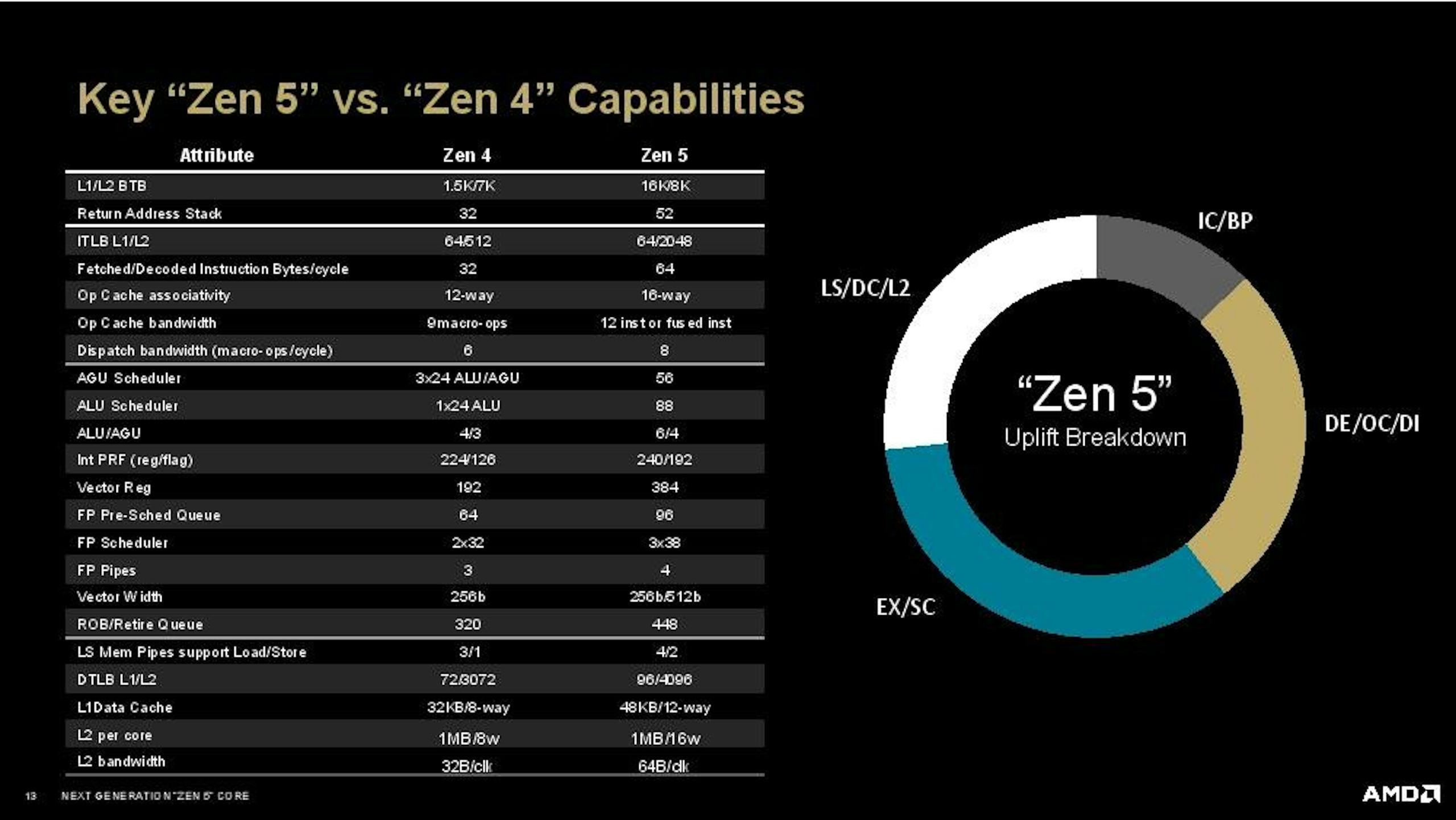

▲Zen 4與Zen 5的關鍵規格比較

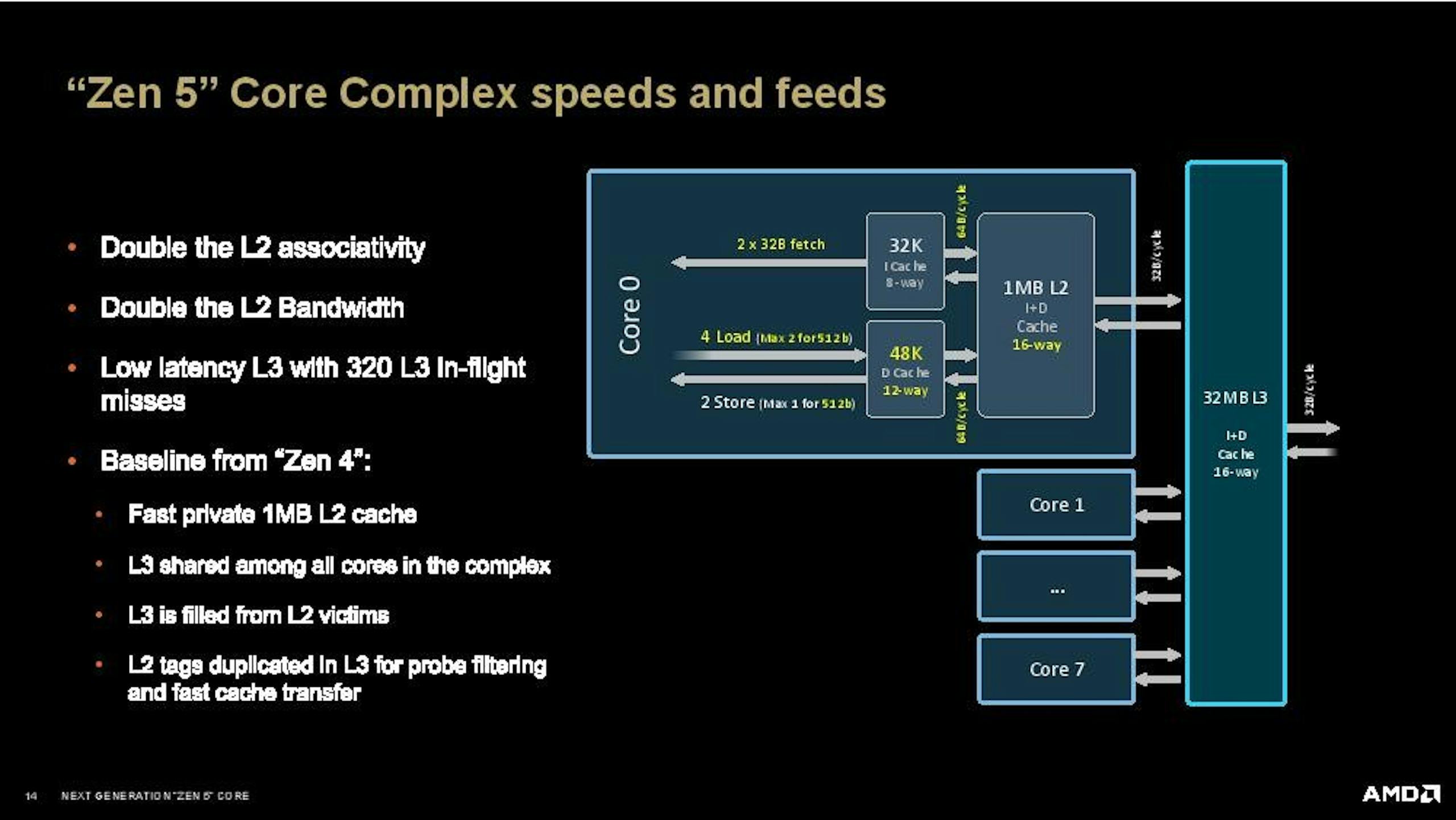

▲透過更高頻寬的L2快取與更低延遲的L3,Zen 5核心具有更強的性能與更低的延遲

Zen 5架構是AMD新一代的CPU核心設計,AMD強調其單執行緒與多執行緒性能都較Zen 4更明顯提升,同時在基本設計理念展望未來,並且為了強化性能與支援更強大的AI運算還支援AVX512;Zen 5同樣提供著重性能的標準版Zen 5與著重能源效率的Zen 5c,此外支援可設定的FP512/FP256路徑,核心設計可提供廣泛的供電支援,且可在4nm與3nm製程生產。

為了實現更出色的性能,Zen 5導入新一代的分支預測架構與更大容量且高性能的快取,並強調仍支援每核心2個執行緒(似乎暗諷Intel為了能耗效率在Lunar Lake的Lion Cove取消超執行緒技術)。另外,Zen 5延續Zen 4每個核心配置獨立1MB L2快取與核心叢集共享L3的概念等特色,但藉由強化L2的關聯與頻寬,還有更低延遲的L3,使多核心群組之間具備更低的延遲,進一步提升多核協作的性能。

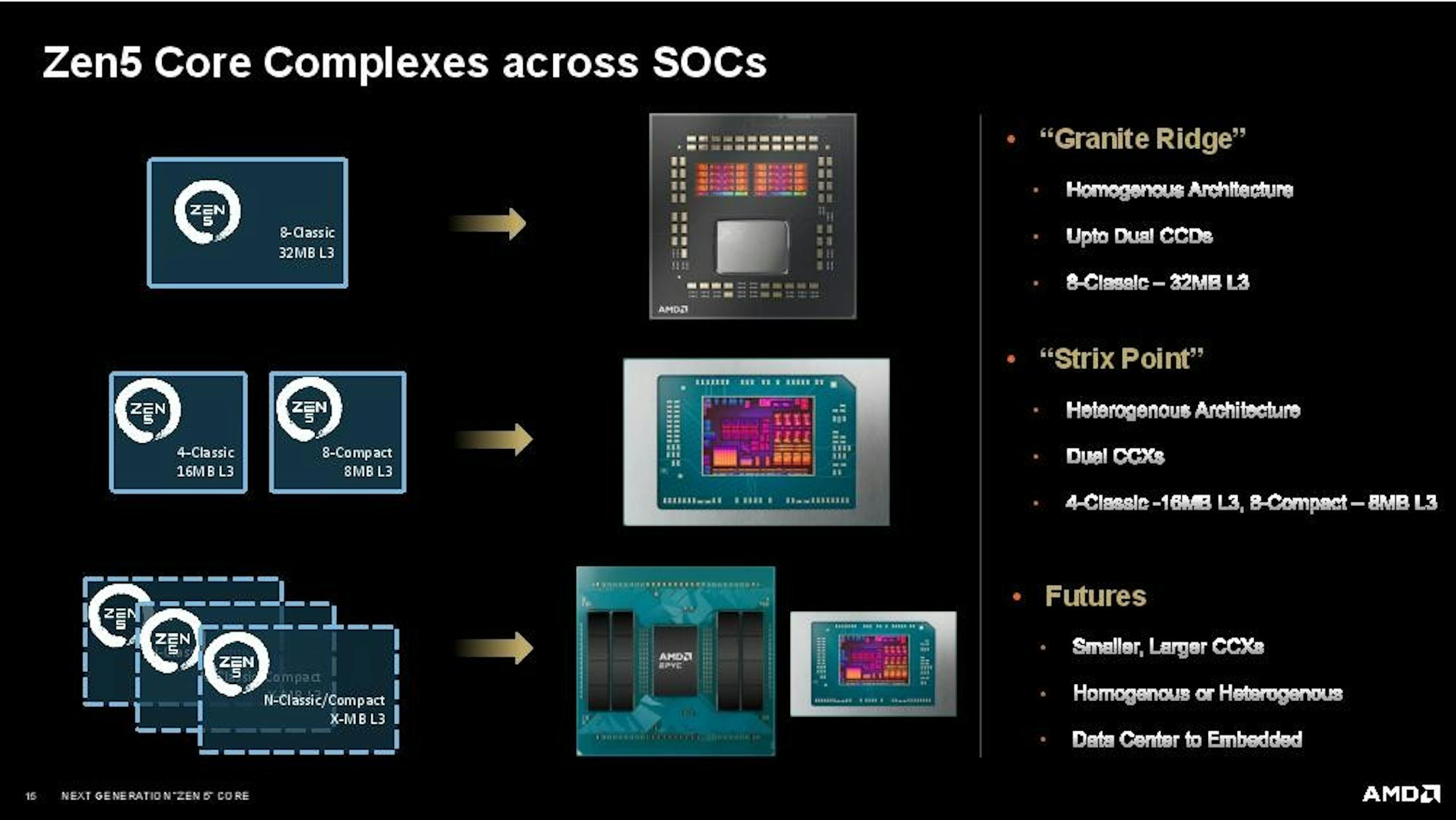

此外AMD也進一步解釋Zen 5與Zen 5c在設計概念的差異,也指出Zen 5與Zen 5c是位於獨立的核心群組,並不會混用在一個群組內;Zen 5著重的是單執行緒效能最大化,著重達到高時脈,並配有大容量的L3快取(在標準設計L3為Zen 5c的兩倍容量);Zen 5c則在保有相同的IPC下進行能源效率與面積占用的最佳化,同時也進一步減少快取;但AMD強調Zen 5與Zen 5c具有相同的架構與IPC,故不會如混用架構的競爭對手遇到如向量效能的瓶頸,也都支援SMT,同時將隨著技術發展將工作更好的在兩種架構之間分配。

▲Zen 5除了消費產品以外也同樣將用於數據中心與嵌入式產品

AMD也不忘強調,除了先行的Granite Ridge「Ryzen 9000」桌上型處理器與Strix Point「Ryan AI 300」行動版處理器兩款消費級產品,Zen 5也同樣會靈活的更小與更大規模的CCX處理器核心模組設計應用在資料中心至嵌入式產品領域。

Strix Point「Ryan AI 300」

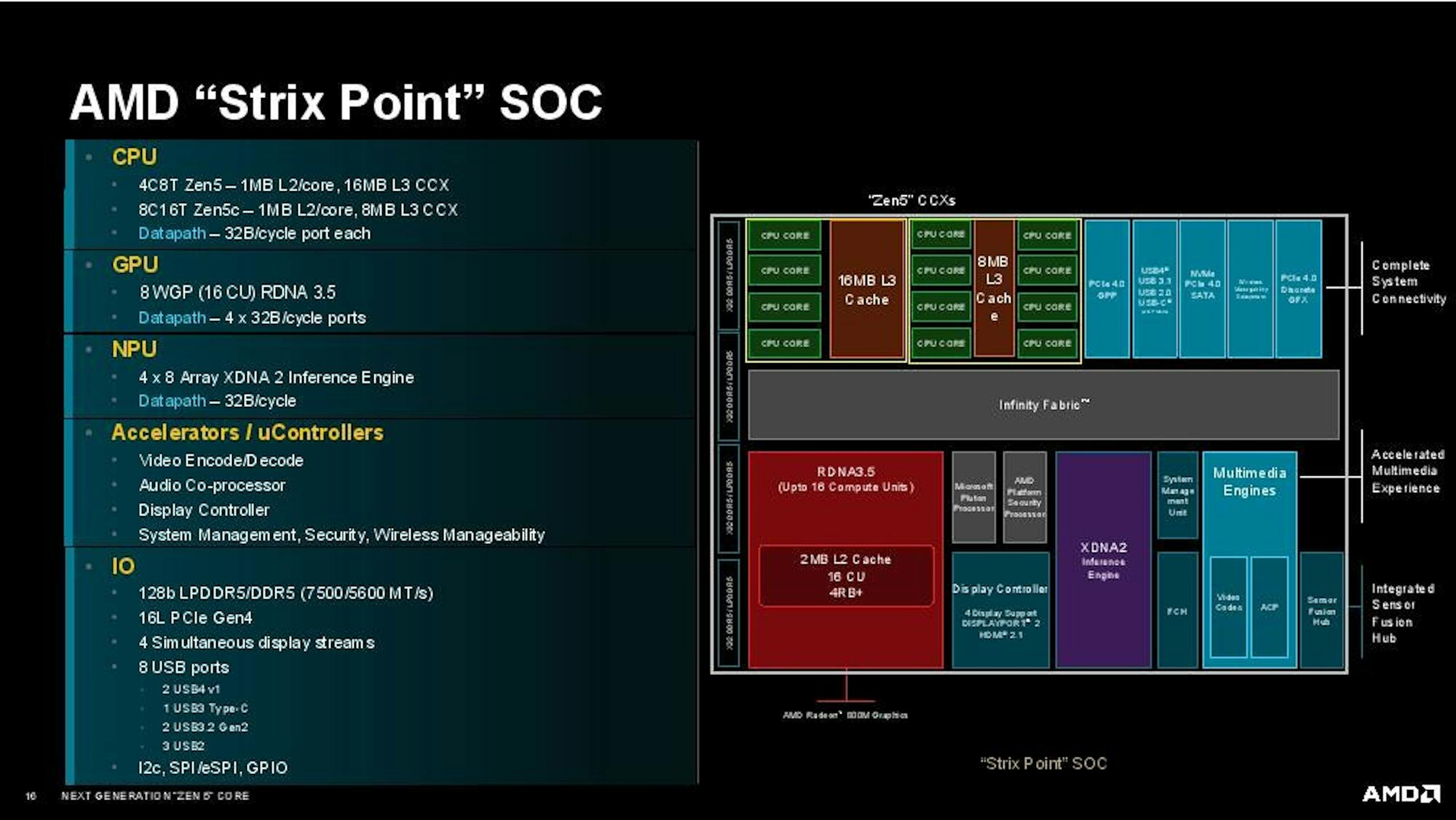

▲Strix Point是專為能源效率最大化設計的架構,由4核Zen 5與8核Zen 5c兩組CCX構成CPU群組

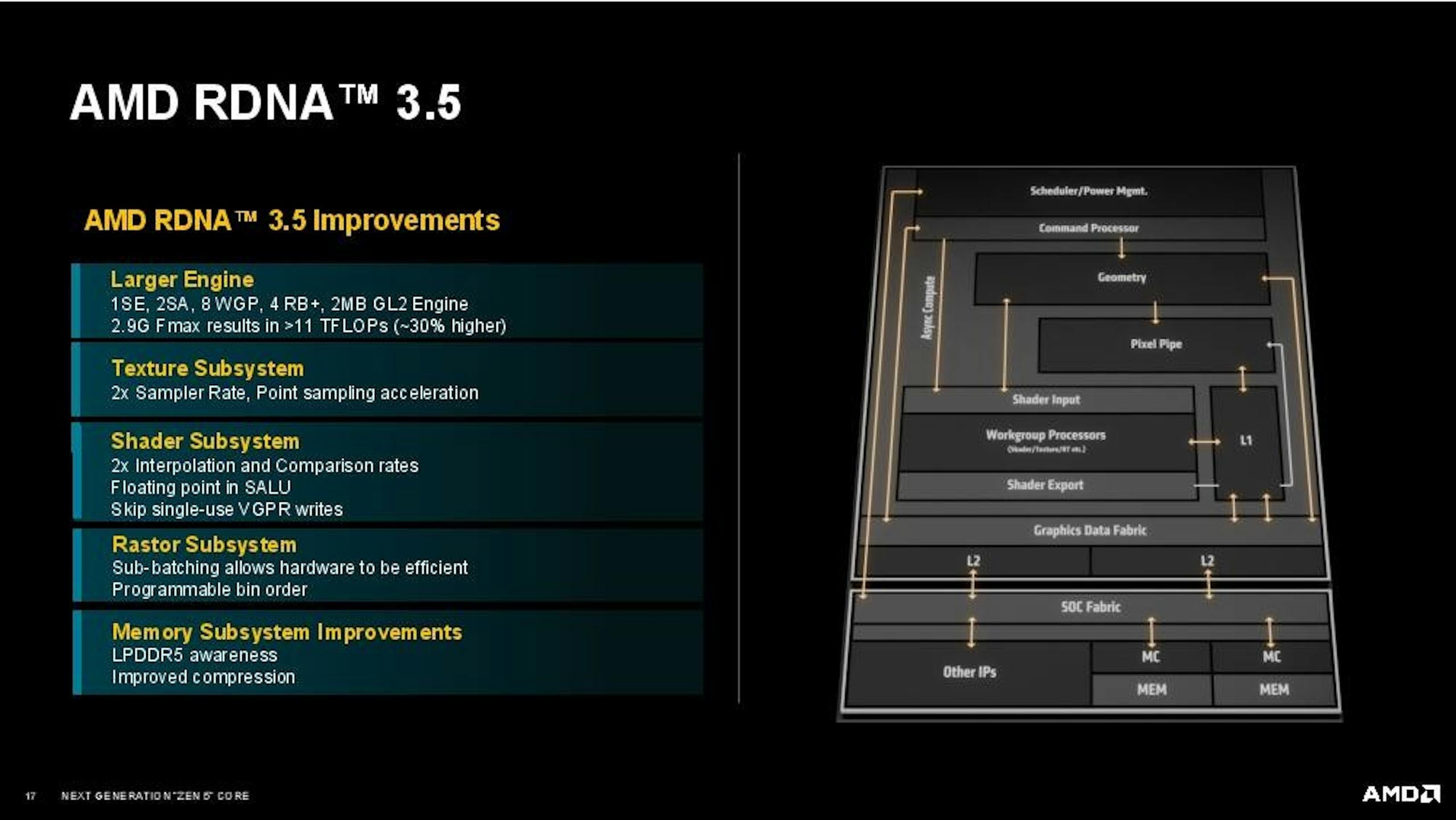

▲RDNA 3.5是取自與三星合作經驗的高能源效率GPU架構

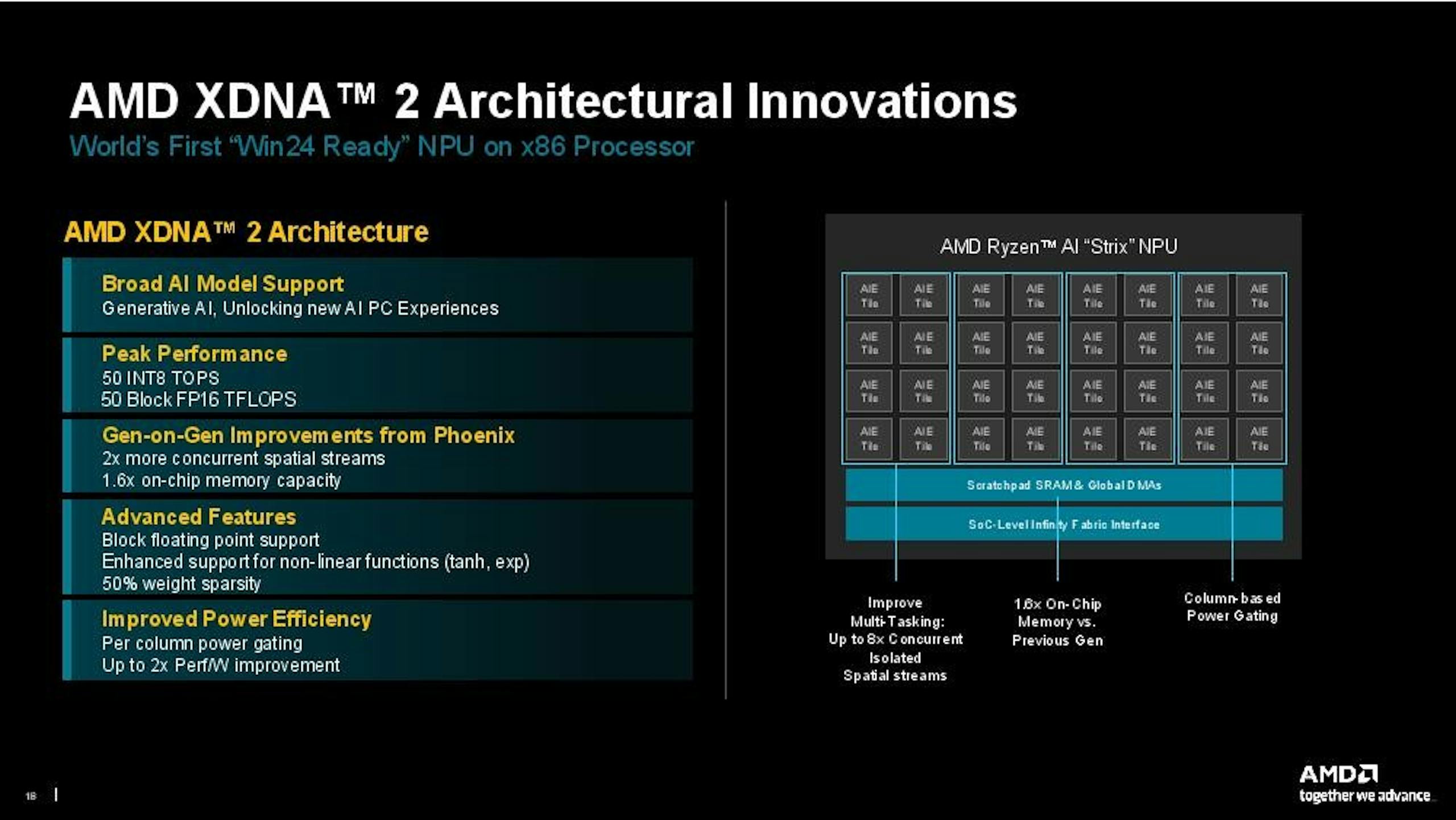

▲XDNA 2提供出色的AI加速性能

在率先亮相的兩款消費級Zen 5處理器當中,AMD對代號Strix Point的Ryzen AI 300系列著墨較多,原因無他,因為Ryzen AI 300是以能源效率最大化為優先進行設計的高度整合SoC,故無論CPU、GPU的概念都是著重如何提供能源效率最大化,同時整合XDNA 2 NPU也是因應當前AI PC趨勢提供更具能源效益的AI使用方式。

此外因應不同性能層級與需求,Ryzen AI 300可支援LPDDR5 7500或DDR5 5600記憶體;通道部分提供16路的PCIe Gen 4,以及支援2組 USB4 v1,一組USB 3 Type-C,兩組USB 3.2 Gen 2與三組USB 2。

Strix Point由兩組CPU的CCX構成,並具備36MB的L2+L3快取;一組為4核心Zen 5的高性能CPU CCX,每個Zen 5具備獨立的1MB的L2,並共享16MB的L3;另一組為8核心Zen 5c節能CCX,每個Zen 5c仍具備1MB獨立L2,不過8核心共享的L3減為8MB。

而Ryzen AI 300系列搭配的RDNA 3.5架構將不會應用於獨立顯示卡,其概念類似於Zen 5c,為針對能源效率最大化的GPU設計,將提供最高8WGP(16CU)配置,在2.9GHz時脈設定下可實現11TFLOPS性能,同時也針對LPDDR5記憶體的特性進行最佳化。

AMD也強調Ryzen AI 300搭配的XDNA 2 NPU是目前性能最強大的CPU整合型NPU,可達50 INT8 TOPS性能與50 Block FP16 TFLOPS性能,是因應裝置端AI應用而設計的能耗效率最大化設計,並相對初代XDNA架構改善一倍的能源效率。

Granite Ridge「Ryzen 9000」

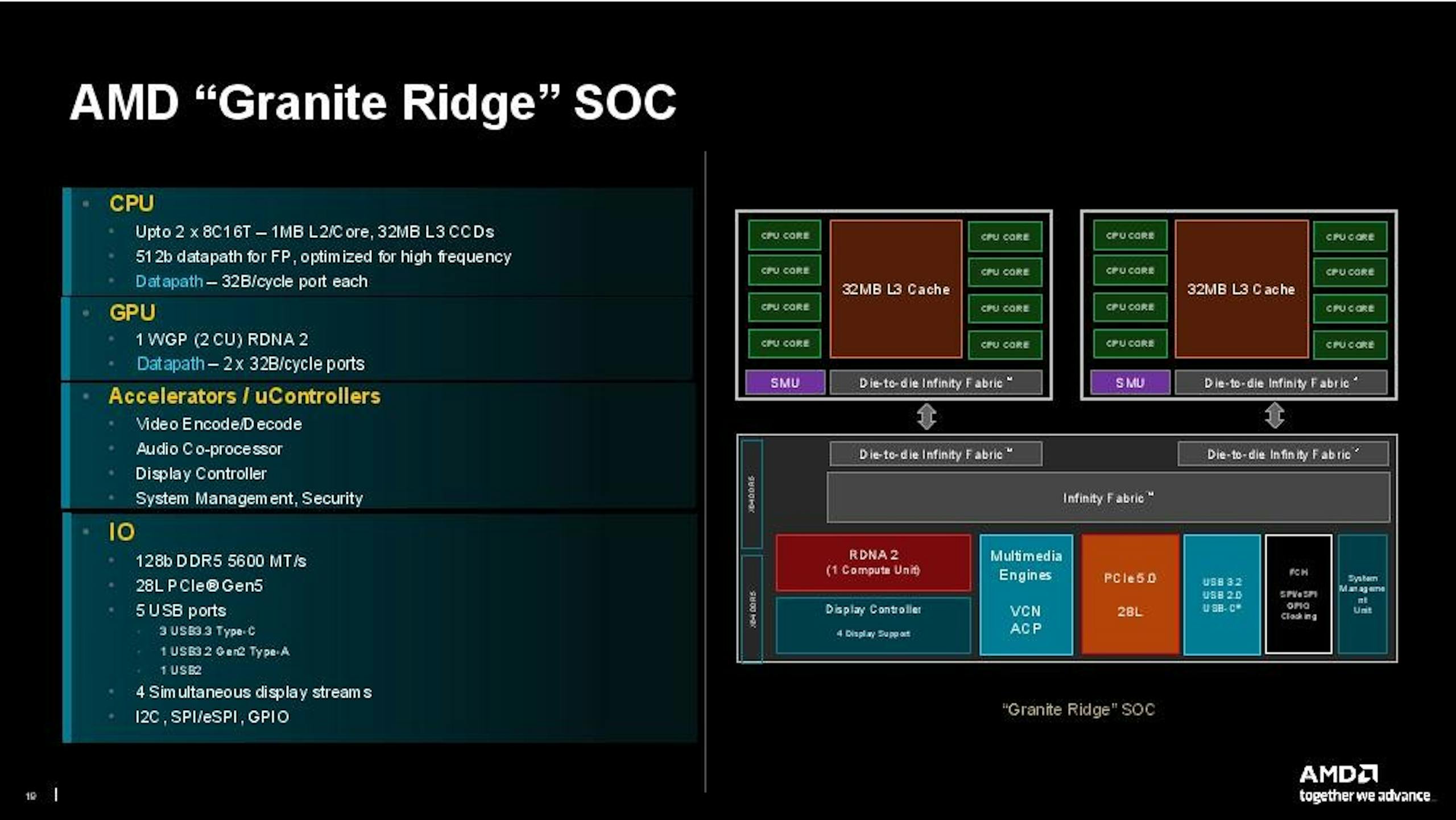

▲Ryzen 9000的設計概念單純許多,由兩組8核Zen 5 CCD搭配Ryzen 7000的管理模組構成

至於桌上型平台Ryzen 9000的設計概念就相對簡單暴力,畢竟AMD現階段定義的桌上型高效能處理器產品線仍以效能最大化為優先,AI則可透過搭配獨立顯示卡實現,AMD為了加速產品開發,故Ryzen 9000並未使用新設計的控制晶粒,而是沿用Ryzen 7000系列的控制晶粒架構,故也不具備NPU,顯示輸出功能仍維持在2CU的RDNA 2架構,僅將CPU CCD更新到Zen 5架構,另外記憶體標準時脈支援則提升至DDR5 5600。

Ryzen 9000的CPU CCX延續Ryzen 7000的每個CCD 8核心配置,最多由2個CCX構成;每個Ryzen 9000的Zen 5核心具備獨立的1MB L2快取,每個CCD具備32MB L3,故在16核心配置下,達到96MB的L2+ L3快取。