如同USB是作為最大宗的公規外接介面,至今已超過20年歷史的PCI Express(PCIe)則是高速I/O匯流排最主要的規格,而PCIe作為背後制定支援合規性與互通性規格與機制的PCI-SIG至今亦有32年的歷史,目前組織成員高達972家,包括AMD、Arm、Dell EMC、NVIDIA、Qualcomm、Synopsys等都是組織成員;此次適逢PCI-SIG於台灣舉辦開發者大會,與PCI-SIG副總裁暨合規性主席Richard Solomon針對PCIe的下一步進展進行專訪。

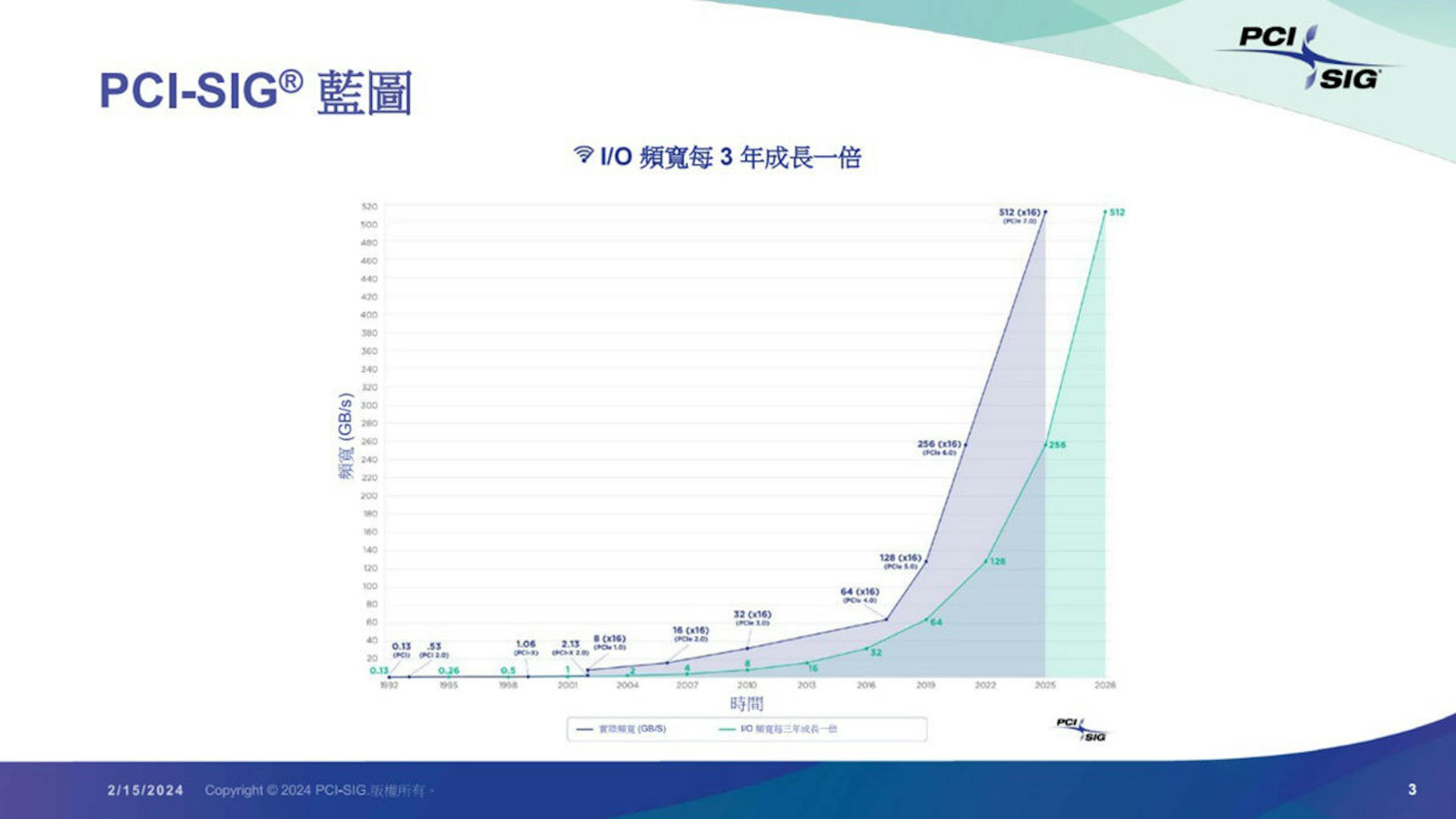

▲PCIe自4.0後由於產業需求增長,也回到3年一個版本、提升2倍速度的節奏

雖然PCIe自PCIe 3.0至PCIe 4.0期間由於產業對高速匯流排需求一度不高而停滯一段時間,然而由於包括晶片對晶片、加速卡、SSD等對於高速匯流排的需求遽增,PCIe每一個版本的性能正以每3年為周期進行翻倍的成長,預期2025年公布1.0規範的PCIe 7.0將頻寬自PCIe 6.0的64GT/s進一步提升至128GT/s,藉此滿足像是資料處理、高效能運算、AI運算等技術對晶片至晶片與儲存至晶片等高速資料傳輸的需求。

授權測試實驗室計畫為成員提供額外的測試管道

▲過往PCI-SIG成員需透過官方合規性工作坊進行測試驗證,2023年底首度由GRL取得授權提供PCIe 4.0的合規性測試服務

為了提升PCI測試認證的效率,PCI-SIG於2023年10月23日推出PCI-SIG授權測試實驗室(ATL)計畫,提供PCI-SIG組織成員除了官方合規性工作坊以外,可藉由授權測試實驗室測試PCIe技術產品並列入PCI-SIG整合商名單的管道,目前由Granite River Labs(GRL)率先取得PCI-SIG授權,可提供PCIe 4.0合規性測試。

相較於PCI-SIG定期、定點舉辦的合規性工作坊,授權實驗室則能提供更即時的服務,但也需支付額外費用,至於為何ALT計畫提供的是成熟版本而非最新版本驗證,則是由於PCI-SIG顧及合規驗證需有完善的程序,最新版本會在建立完善的驗證與除錯程序後才提供給認證實驗室;PCI-SIG也預計透過與GRL的合作經驗為基礎,計畫後續提供更多認證實驗室。

PCIe 7.0預計2025年公布規範、合規計畫與終端預計2028年問世

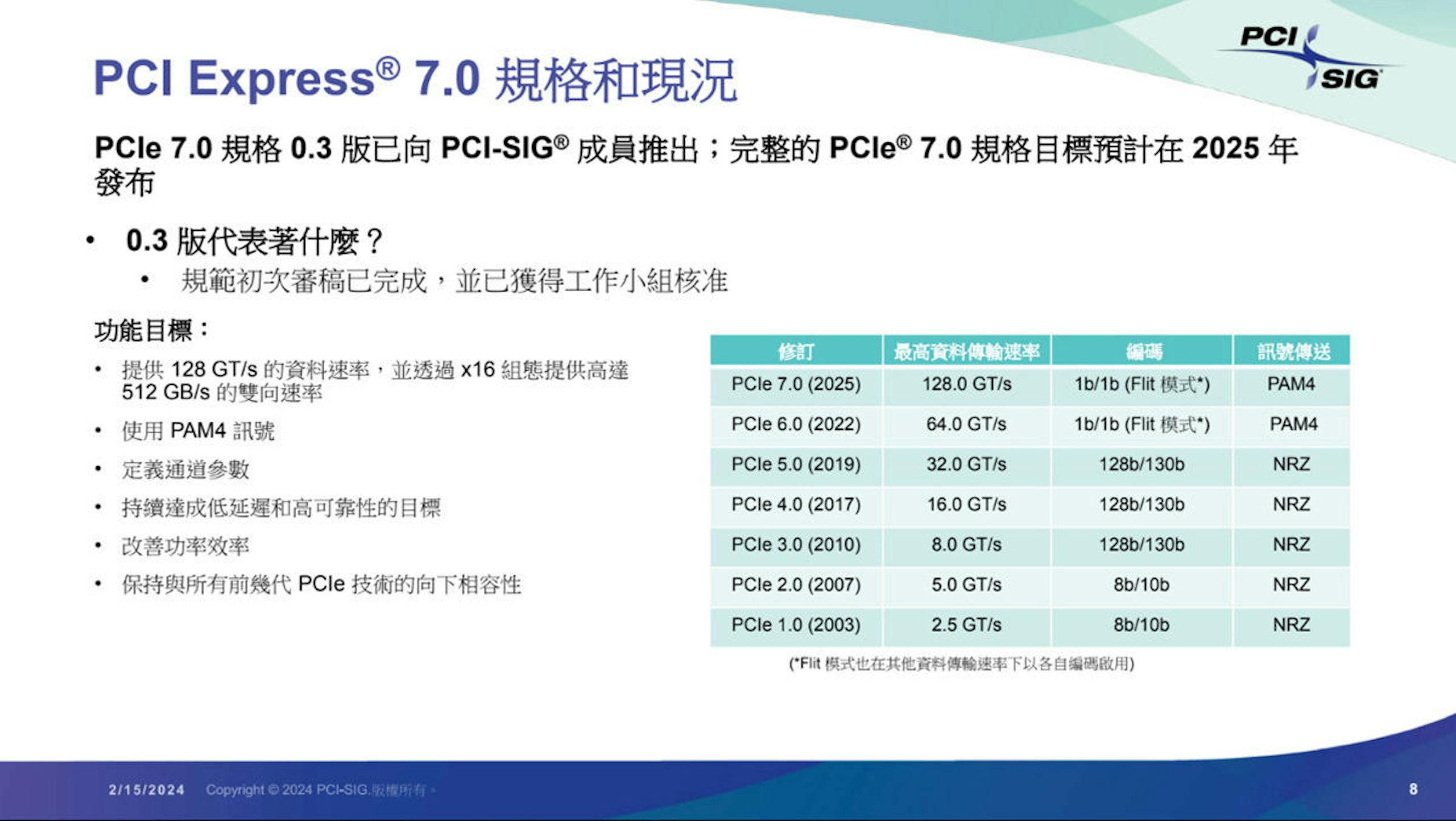

▲PCIe 7.0預計在2025年頒布1.0規範,但合規計畫理論上要至2028年

為了使業界能夠有充裕的時間進行,PCI-SIG也自規範公布至和規計畫提供3年的追蹤期,而早期產品可在合規計畫日期前開始供應,不過多半合作夥伴都會待到合規計畫日期後才推出產品,以2022年1月公布的PCIe 6.0,2024年第2季就將邁入初步合規計畫、2025年公布整合商名單;做為下一個版本的PCIe 7.0目前已經進入0.3版,預計在2025年公布1.0版、2028年合規計畫上線,是故Richard Solomon表示此次PCIe 7.0並未有太多新消息。

▲PCIe 7.0將延續PCIe 6.0的訊號傳送與編碼方式

在PCI-SIG的0.3版,意味著PCI-SIG已將PCIe 7.0的規範完成初次審稿,同時獲得工作小組批准;目前的目標功能除了將保有技術向下相容性,將以128GT/s的資料速率為基礎、透過x16組態實現512GB/s雙向速率,技術上採用與PCIe 6.0相同的PAM4訊號,並定義通道參數,達成低延遲、高可靠的目標,同時改善功率效率。

由光學專家另行成立光學工作小組,旨在提供長距離傳輸與探索未來的可能性

同時為了不斷增長的匯流排頻寬需求,PCI-SIG也自2023年8月2日成立光學工作小組,光學工作小組探索透過光纖互連的匯流排願景;PCI-SIG光學工作小組的目的是支援廣泛的光學技術,並開發適用於特定技術的外型尺寸,其中包括可插拔光學收發器、板載光學元件、共同封裝光學元件與光學I/O等。

由於PCIE-SIG既有小組成員專精於銅纜傳輸技術,故既有的PCI-SIG小組將持續朝PCIe 7.0定義的128GT/s邁進,由光學傳輸技術專家組成的光學工作小組將致力於使PCIe架構更光學友善,為PCIe提供於銅纜與光學作為載體的技術一致性與互通性。

當前預期PCI-SIG將使用相同元件(如預期使用相同的Flit模式、相同的鏈路調訓)確保最少變更,潛在規格增強則包括根據光測協調速度轉換、使邊待訊號處於帶內、使規格更加截能、擴大覆蓋範圍等。目前PCI-SIG對於光學傳輸還未有明確的方向,但初步將為遠距PCIe傳輸與容易干擾電訊號的環境提供新選擇,也為了不知何時到來的銅纜傳輸門檻做準備。

CooperLink 5.0/6.0將為連接型態帶來創新

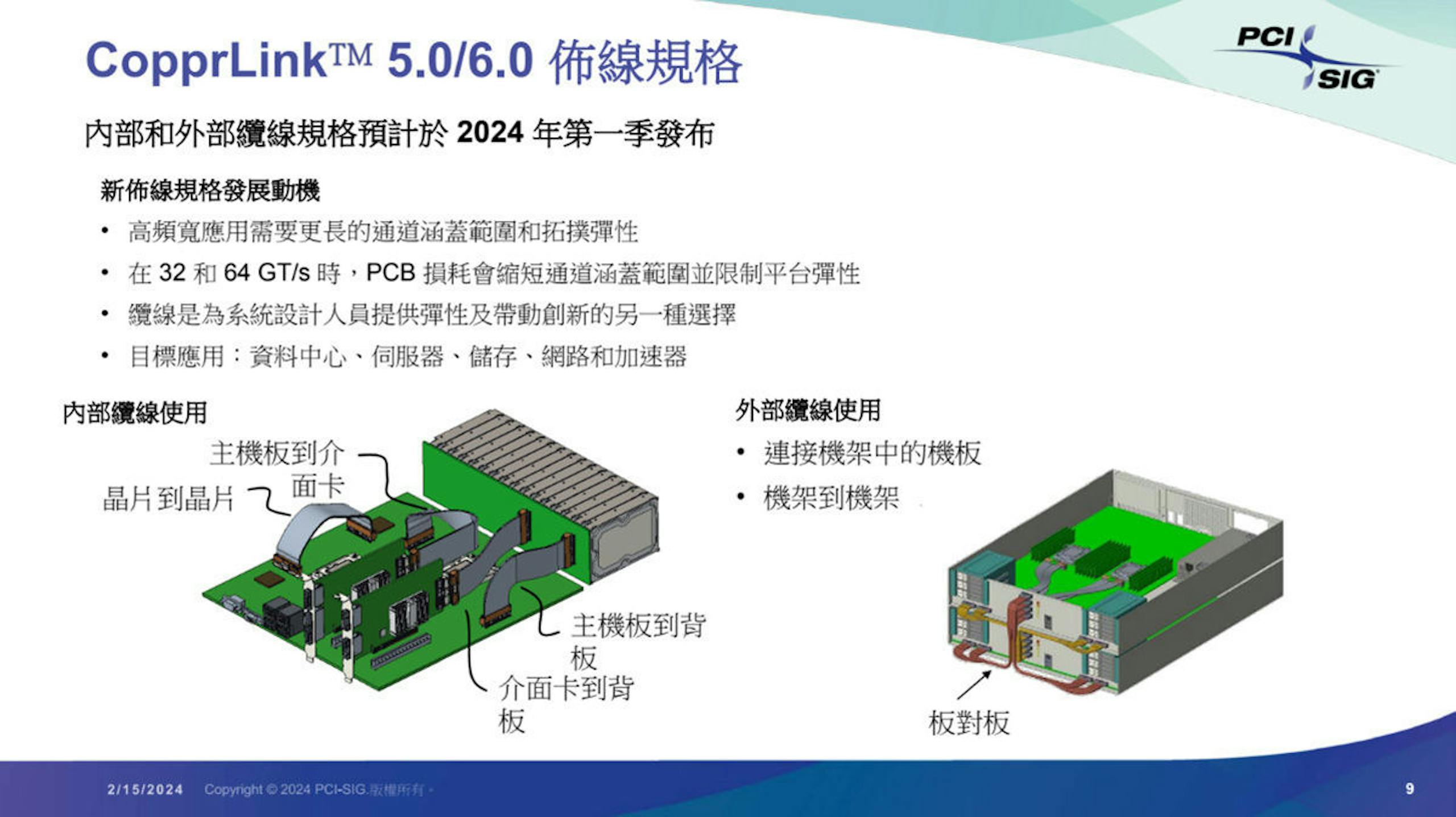

▲CooperLink 5.0/6.0佈線規格有望為系統佈線與跨機佈線帶來變革

另外,PCI-SIG也將在2024年第一季宣布CooperLink 5.0/6.0的內部與外部纜線規格,由於因應頻寬增長一倍,需要更長的通道涵蓋範圍與拓樸彈性,於32GT/s與64GT/s時,PCB耗損會縮短通道涵蓋範圍與限制平台彈性,而纜線則提供系統設計人員彈性與創新的選擇,CooperLink 5.0/6.0初期將將應用於資料中心、伺服器、儲存、網路與加速器領域,短時間不會在消費市場亮相。

AI與運算固然是驅動高速PCIe需求的主力、但自駕技術也意外的需要更高頻寬

▲台灣的開發者大會於2024年2月19日與20日之間在台北萬豪酒店舉辦

Richard Solomon提到,目前驅使PCIe規格革新的關鍵在於如高速運算、小晶片、AI等趨勢,作為業界通用規範的PCIe技術也針對這些需求不斷加緊腳步投入下一代規格制定,其中在晶片對晶片,與高速儲存裝置的連接,還有節點與節點之間的高速連接等領域,都是追求更高速的通用匯流排技術的原動力。

不過以自動駕駛為關鍵的車載也對高速匯流排有相當大的需求;自動駕駛平台猶如在車上安裝一套微型的超級電腦,同時連接到大量的感測器進行龐大數據的資料串流,又對低延遲相當的敏感。高速匯流排不僅提供更高的頻寬與低延遲,同時對於著重可靠性的車用電子,能夠在具備高速頻寬環境傳輸較小的數據量,反而有助資料傳輸的穩定。

此外,PCIe每版本提升一倍的頻寬特性,也能提升連接佈署的彈性,畢竟等同下一代的規格僅需當前世代一半的通道就有相同的理論傳輸性能,對部分應用等同可減少通道的使用,例如目前消費級PCIe 5.0 SSD就已有廠商利用PCIe 5.0高於PCIe 4.0一倍頻寬的特色,推出在PCIe 5.0模式僅使用x2通道的產品

企業級SSD儲存將是PCIe 6.0首波的主要產品之一

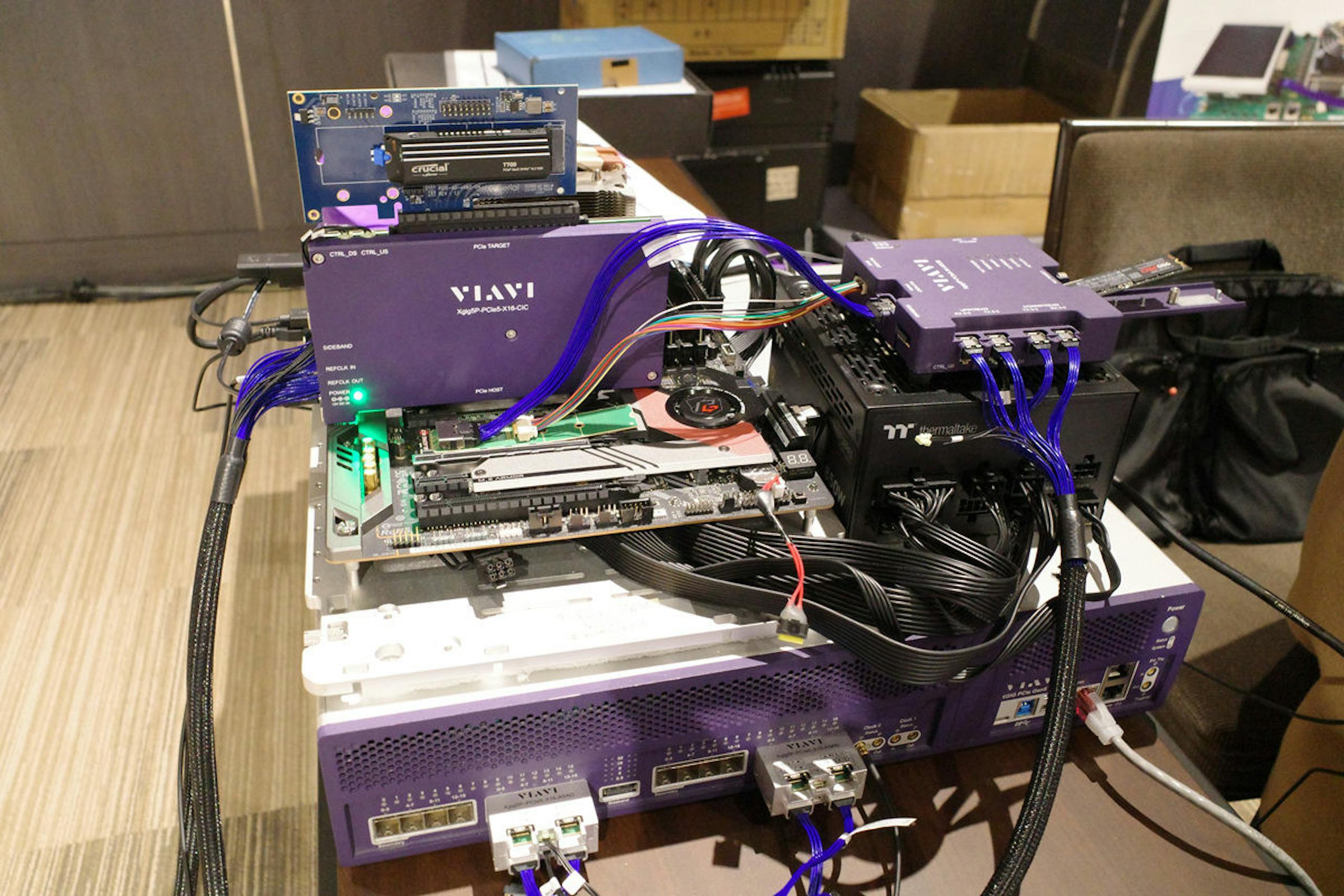

▲翔宇科技代理的VIAVI Solution電腦運算匯流排解決方案可供測試PCIe 5.0與PCIe 6.0儲存設備

在訪談後筆者也拜訪在開發者大會展示技術的PCI-SIG合作夥伴,不過由於時間接近首日活動結束,許多廠商的服務人員已經先撤場,但Richard Solomon提到雖然PCIe 6.0要至2025年才會公布整合商名單,不過當前已有許多PCI-SIG成員積極投入產品驗證測試。

筆者在展示區與展示VIAVI Solution電腦運算匯流排解決方案的台灣代理商翔宇科技簡單聊過,表示目前已有許多針對企業級的儲存產品投入PCIe 6.0規格產品的測試驗證,畢竟相較消費級產品的使用形式與傳輸性能需求,對多數的使用者甚至感受不到PCIe 3.0提升至PCIe 4.0的差異,但更高的成本與發熱使得新一代的PCIe 5.0儲存在消費市場仍未普及;反而對於資料量日益龐大的資料中心、超級電腦等,則可顯著受益於PCIe 6.0規格帶來的頻寬與低延遲。