小晶片 Chiplet 與多元晶圓代工是現在晶片產業的新趨勢,借助小晶片技術能夠降低設計複雜度、提升生產良率具備更高的設計彈性,當小晶片結合多元晶圓代工則可因應製造成本、技術等由合適的晶圓廠生產晶粒,然而要提升小晶片設計的彈性,就需透過通用協定使不同的晶粒得以順利溝通,是故 Chiplet Interconnect Express ( UCIe ) 通用協定也順應而生; Intel 在 2023 Intel Innovation 展示新一代 Intel 3 製程的同時,由執行長 Pat Gelsinger 展示一顆以 UCIe 結合 Intel 3 製程晶粒與台積電 N3E 製程晶粒的測試晶片。

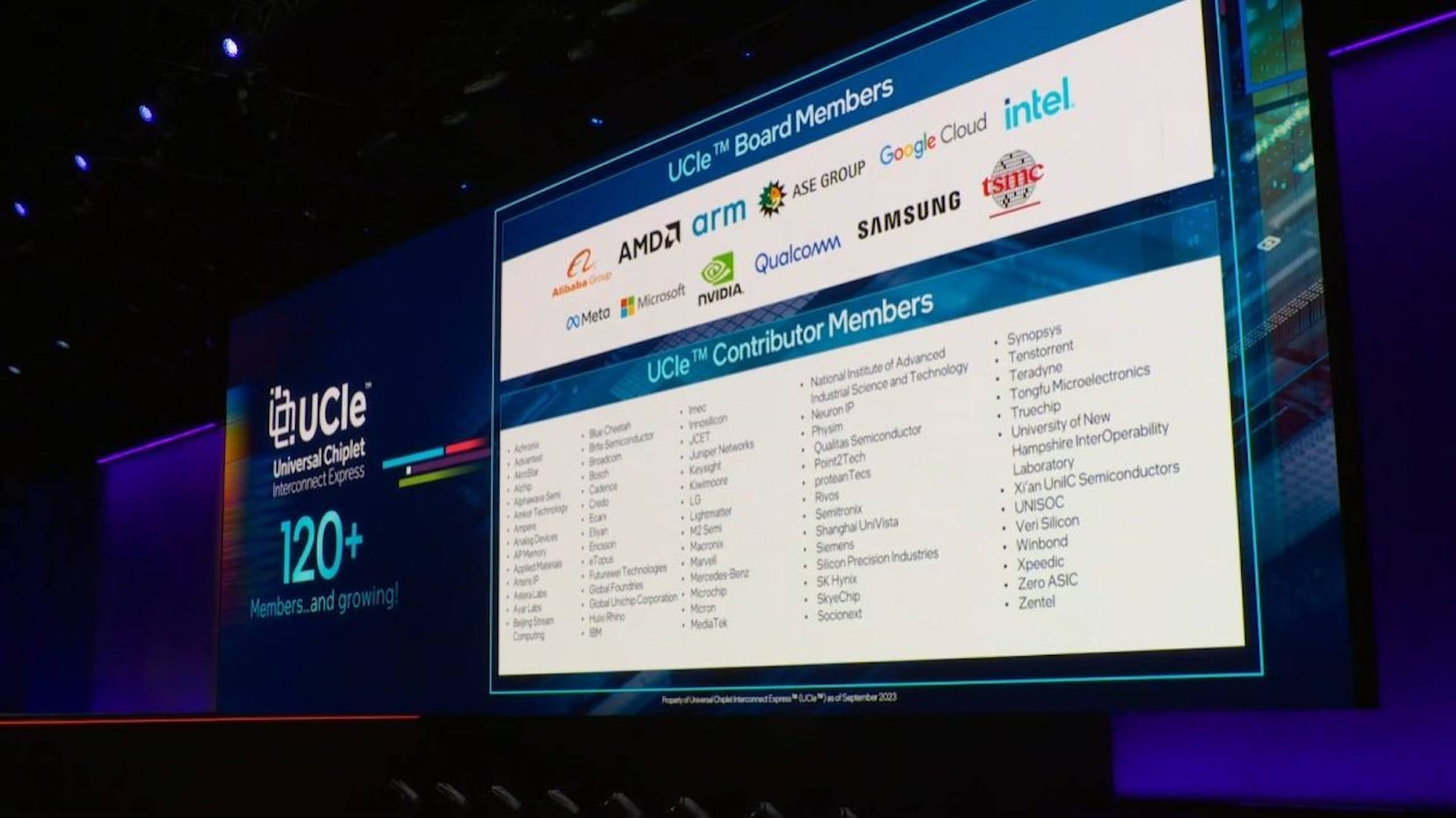

▲ UCIe 獲得超過 120 家半導體相關產業夥伴的支持,將作為驅動小晶片發展的重要協定

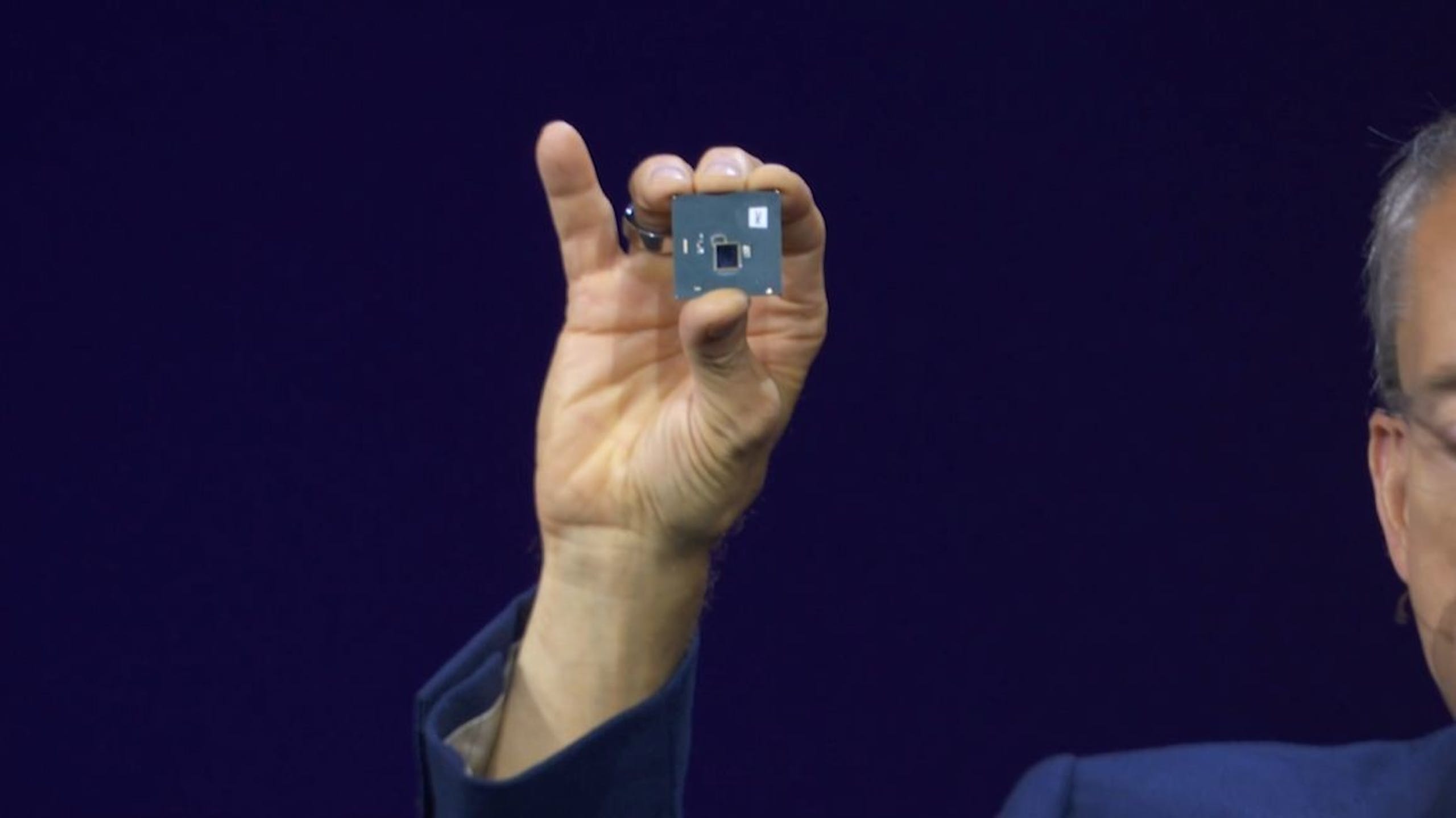

▲此次展出的測試晶片結合 Intel 3 與台積電 N3E 製程的小晶片晶粒,透過 Intel EMIB 封裝技術連接

Intel 3 製程預計在 2023 年底完成,此次的展示可說是 Pat Gelsinger 先前於 IDM 2.0 喊出 Intel 將在 4 年實現 5 個製程節點以及彈性使用多元晶圓代工的體現; UCIe 規範在 2022 年制定,並有超過 120 家半導體相關產業夥伴支持,此測試晶片結合 Intel 3 製造的 Intel UCIe IP 小晶片與 TSMC N3E 製造的 Synopsys UCIe IP 小晶片,透過 Intel EMIB 先進封裝進行連接。

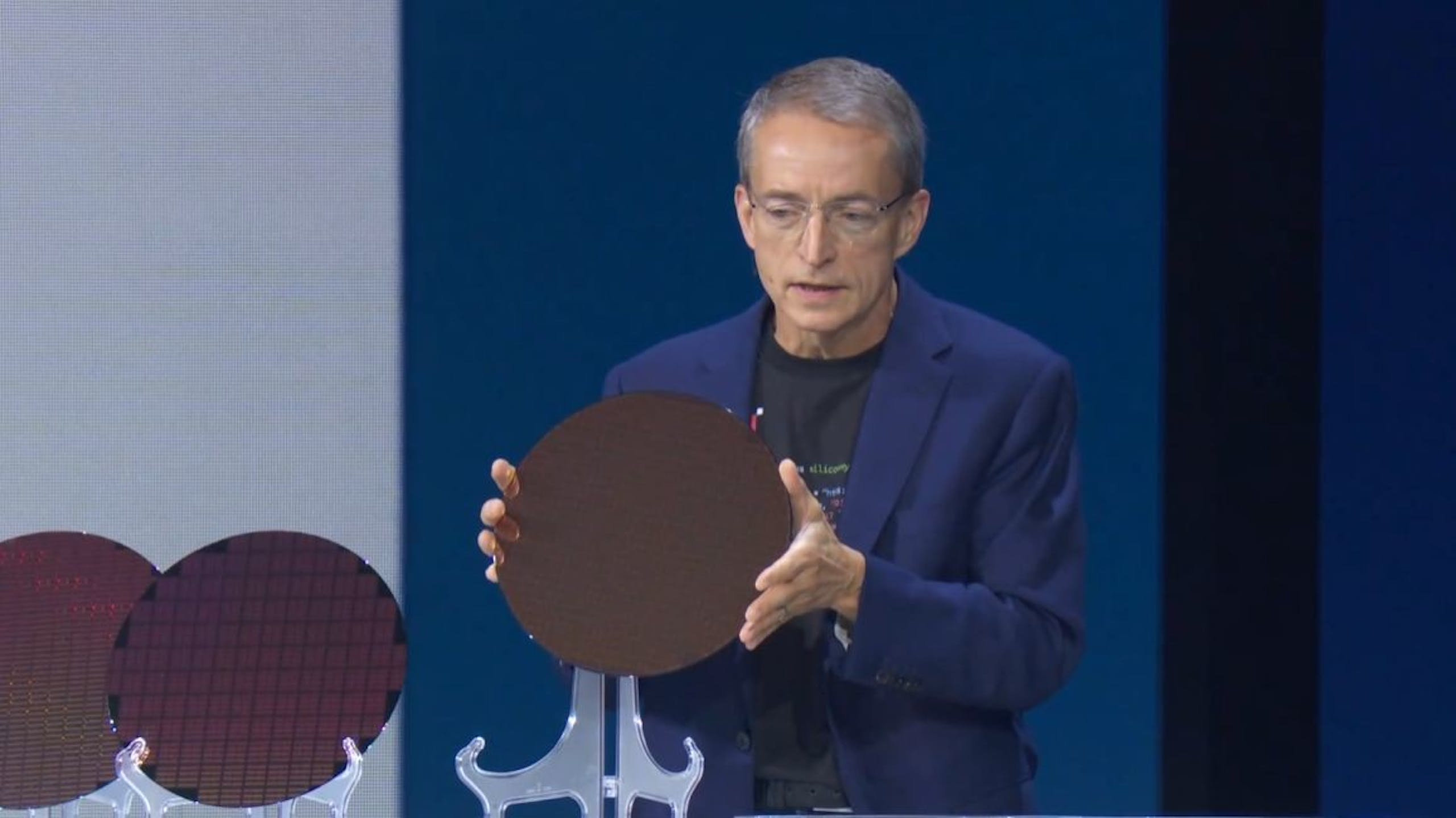

▲ Intel 20A 製程將首次導入背面供電 PowerVIA 與 RibbonFET

此外作為 Intel 3 之後的展望, Pat Gelsinger 也展示基於 Intel 20A 製程的 Arrow Lake 晶圓, Intel 20A 將實現 PowerVia 背面供電技術,同時也將導入 RibbonFET 環繞式閘極設計,而預計於 2024 年下半年投產的 Intel 18A 也同樣具備 PowerVIA 背面供電以及 RibbonFET 環繞式閘極設計。