Intel 在 2021 年 7 月除了公布全新的電晶體架構 RibbonFET 以外,也宣布獨創的背面供電技術 PowerVIA ,透過將供電架構自晶圓正面佈線轉移到背面進行直接供電,將晶圓上部全部用於訊號傳輸,結果即是使電晶體開關速度增加,同時能夠在更小的面積占用實現與多鰭片設計同等的驅動電流;在 IEEE 舉辦的 VLSI 2023 研討會前夕, Intel 將展示 PowerVIA 的實作。

#VLSI2023 Highlight paper T1-1 “E-Core Implementation in Intel 4 with PowerVia (Backside Power) Technology” – Intel Corp.

— IEEE Symposium on VLSI Technology and Circuits (@VLSI_2023) May 2, 2023

Intel reports a high-yielding backside power delivery technology, PowerVia Technology*, and Intel E-Core Implementation in PowerVia Technology. pic.twitter.com/0us9rbUvQr

▲左邊違現行供電位於電晶體上方、使供電與訊號需交錯的設計,左方的 PowerVIA 將供電轉移到下方直接供電、使晶圓上方僅存訊號線路

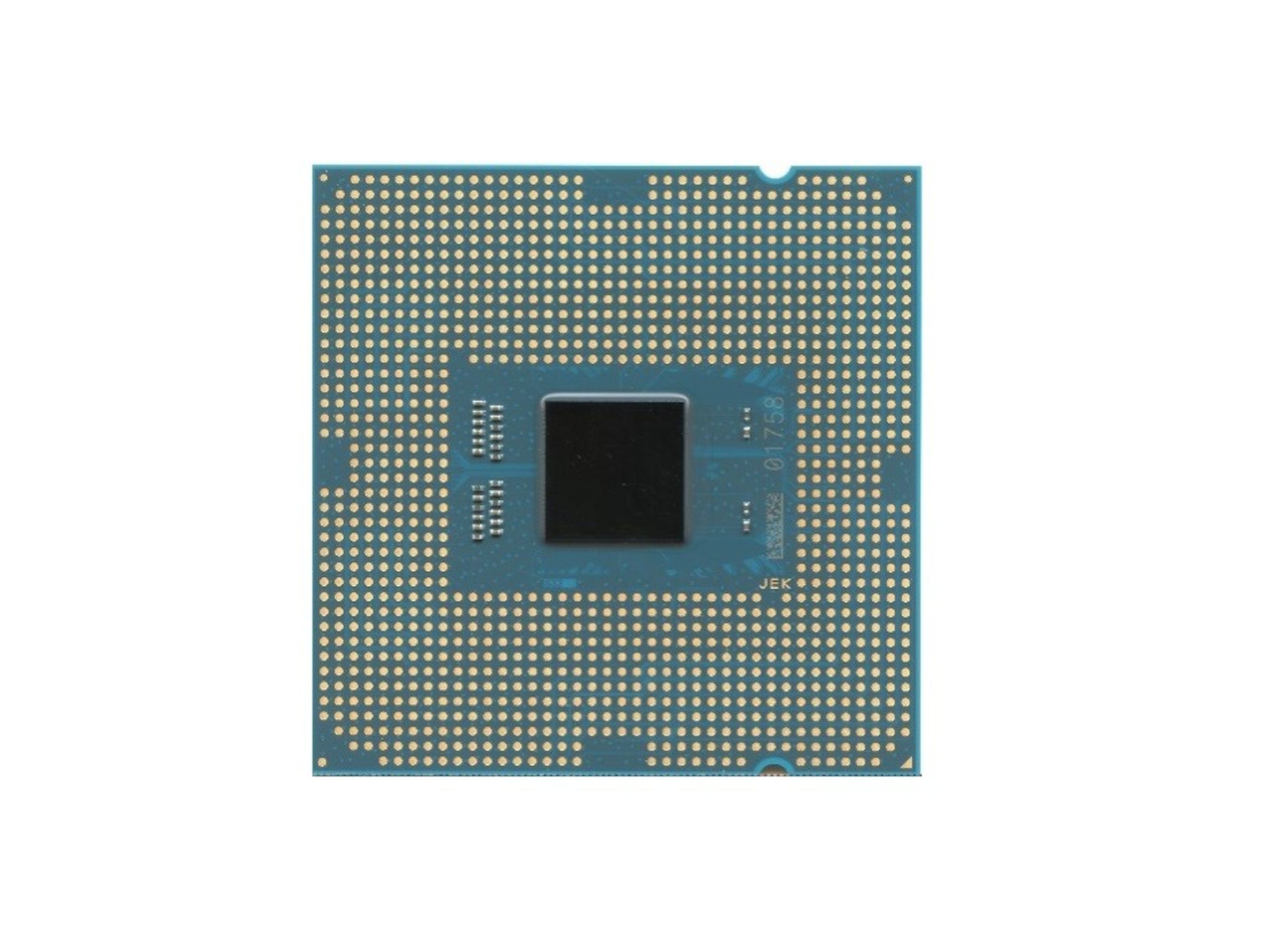

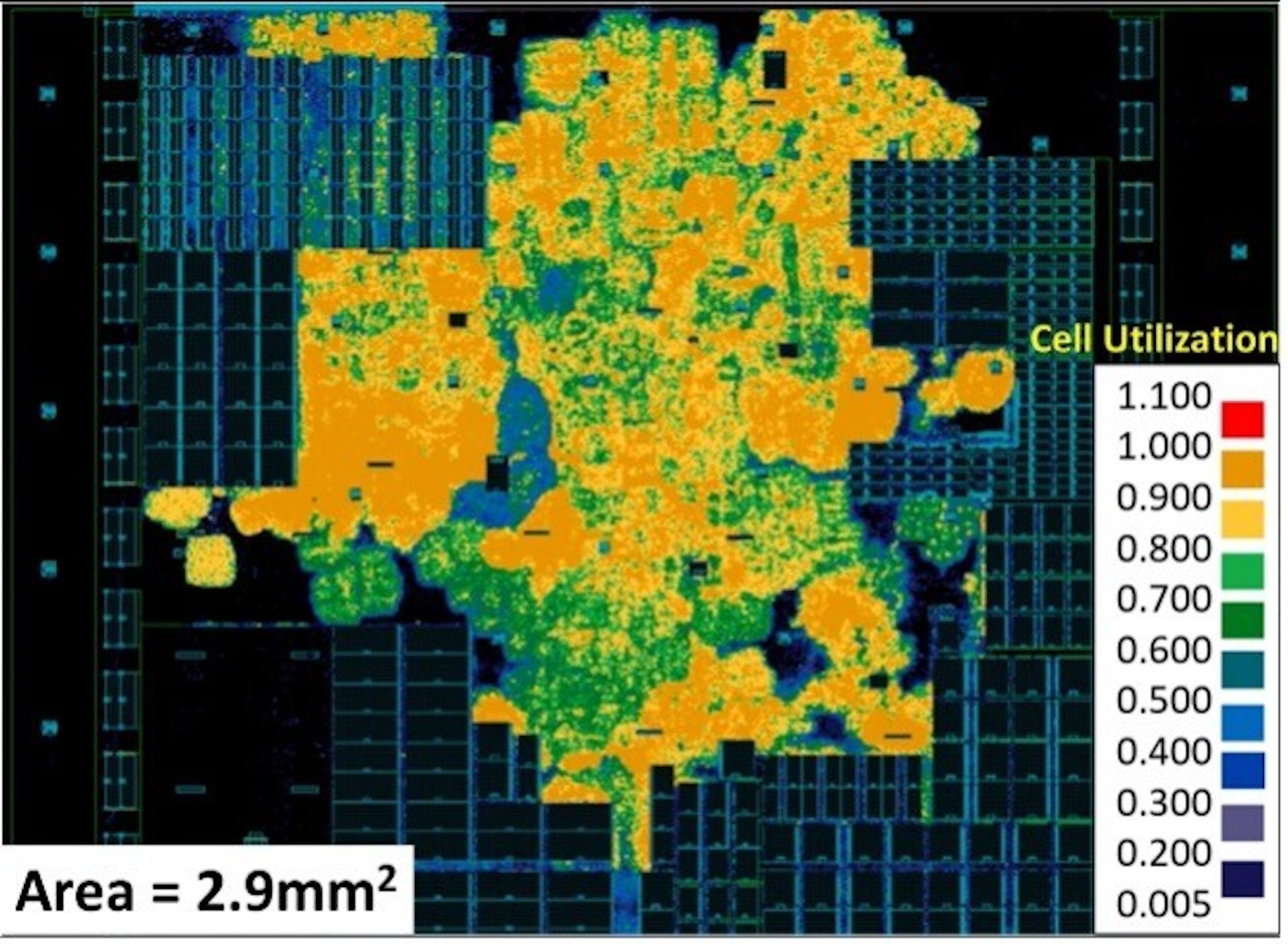

在 VLSI 研討會官方推特的預告中提到,這是一顆採用 PowerVIA 全 E Core 的 Intel 4 製程晶片,從針腳設計酷似已經淘汰的 LGA 1200 針腳,最大的不同是原本現行 Intel 晶片中央背面佈滿 SMD 電容的位置被 PowerVIA 技術的晶粒取代;根據目前公布的資料,在 2.9mm2 的面積,能使能源使用效率達到 90% 並減少 IR 降壓,最終的結果是使時脈提高 5% 。

▲ PowerVIA 相較傳統晶圓上部供電能提升能源效率並提高 5% 時脈

不過此次主要是針對 PowerVIA 的進行實作展示,根據 Intel 的規劃, PowerVIA 並不會使用在 Intel 4 製程,至少要等到導入 RibbonFET 架構的 Intel 20A 與 Intel 18A 製程後才會用於消費級晶片,據稱 PowerVIA 技術最快將在 2024 年出現在消費終端市場。