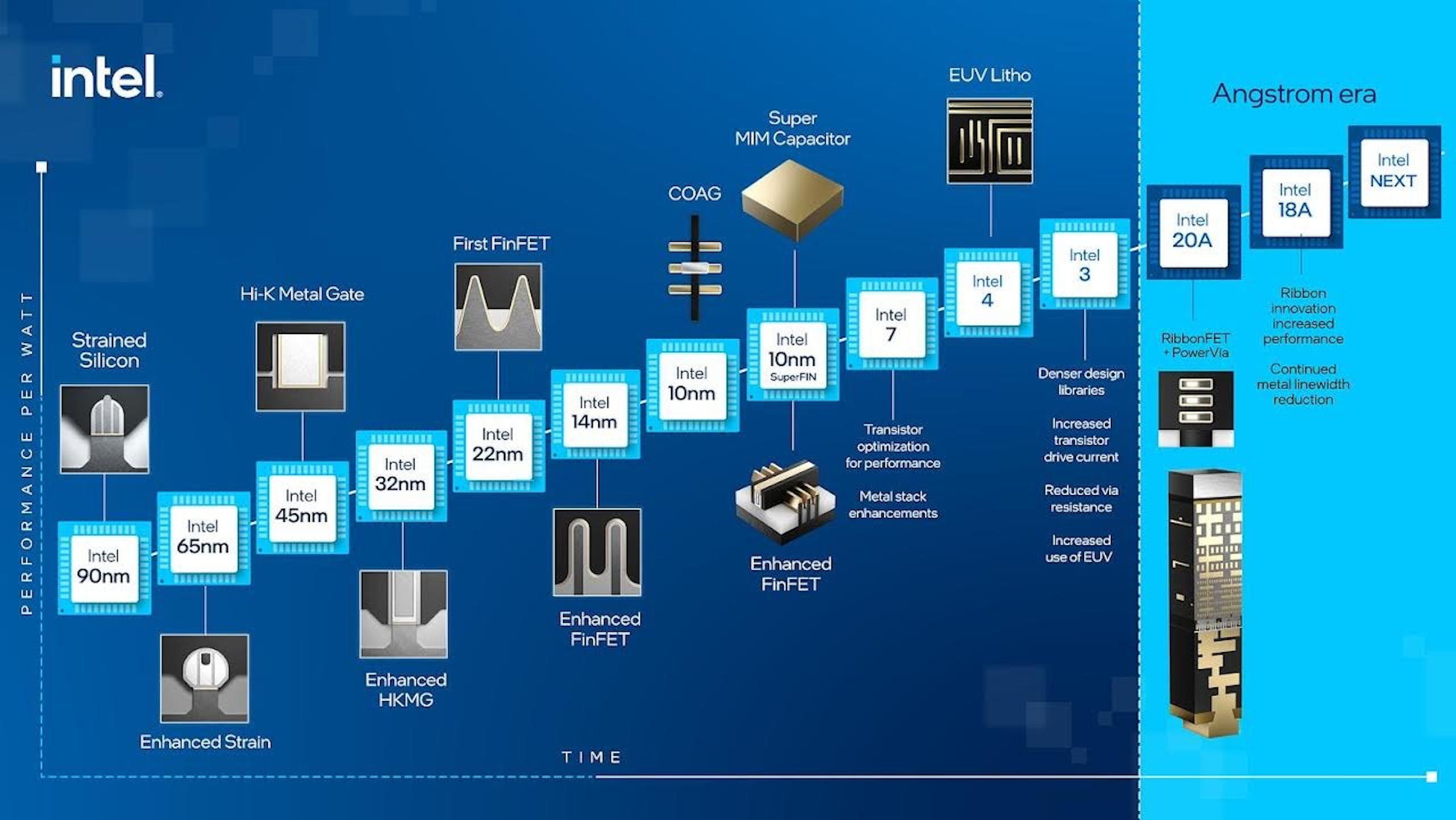

Intel 在近日於美國檀香山舉辦的 VLSI 國際研討會公布下一代製程 Intel 4 的技術細節, Intel 4 預計在 2023 年投入產品生產,並預計使用在包括消費端的 Meteor Lake 等在內的新平台,同時可推進先進技術與製程模組的領先地位,併希冀在 Intel 4 推出後,於 2025 年再度回歸製程技術領先; Intel 強調相較借助專為高效能先進運算的 FinFet 製程, Intel 4 將較現行 Intel 7 在相同功耗提升 20% 以上效能,同時高效能元件庫( Library Cell )密度提升兩倍。

Intel 在將 14nm 製程玩到爐火純青後,面對競爭對手以台積電先進製程加持的挑戰,在技術老將 Pat Gelsinger 自 VMWare 回鍋擔任執行長後,積極回歸以先進製程開發的傳統 Intel 發展路線的 IDM 2.0 計畫,並且制定製程發展藍圖以及部分製程委外的混合生產、跨製程混合封裝技術、開放晶圓代工等計畫,希望能迎頭趕上台積電、最終重返製程霸主的偉業。

Intel 藉助於 Intel 4 的鰭片間距、接點間距與低層金屬間距等關鍵尺寸進行微縮,並導入設計技術偕同最佳化,藉此縮小單一元件尺寸;透過 FinFET 材料與結構上的改良, Intel 4 單一 N 型半導體或 P 型半導體的鰭片數量相較 Intel 7 高效能元件庫的 4 片減為 3 片,使邏輯元件密度提升並縮減路徑延遲,同時帶來功耗降低的優點。

Intel 自基於 Intel 10nm 的 Intel 7 製程導入自對準四重成像技術( Self-Aligned Quad Patterning / SAQP )與主動元件閘極上接點( Contact Over Active Gate / COAG )技術提升邏輯密度,結合 SAQP 單次微影與兩次沉積、蝕刻步驟使晶圓微影圖案縮減四倍,此外也沒有多次微影層疊對準問題, COAG 則是將閘極接點設於閘極上方,相較傳統把接點設於閘極一側可提升元件密度; Intel 4 除承襲這兩項關鍵技術,再加入網格布線( Gridded Layout Scheme )簡化與規律化線路,使效能、良率雙雙提升。

▲ Intel 4 進一步將 EUV 自最關鍵層擴大使用到較高互連層

面對製程持續微縮,電晶體上方金屬導線接點縮小也帶來更多挑戰, Intel 4 製程也同樣需克服導線電組與線路直徑呈現反比帶來的效能流失問題,因此 Intel 使用稱為強化銅 ( Enhanced Cu )的金屬配方取代目前 Intel 7 的鈷,強化銅以銅做為導線與接點為基底,外層加上鈷、鉭包覆,能兼具銅的低電阻與降低自由電子移動的撞擊原子位移導致電路失效的電遷移( electromigration )現象,將作為下一世代 Intel 3 以及未來製程的基礎。

EUV 是目前先進製程廣泛用於簡化製程的技術, Intel 在當前的技術的最關鍵層使用 EUV ,而 Intel 4 則把 EUV 技術擴大到較高互連層,可進一步減少光罩數量與製程步驟,可減低製程複雜性, Intel 也強調會在未來製程更廣泛採用 EUV 技術,同時也將導入渠球第一款量產型高數值孔徑( High-NA ) EUV 設備。

2 則回應

Intel 7 是使用 10nm技術 , 舊名為10nm Enhanced Super Fin 或 10ESF

Intel 4 是使用 7nm技術 , 舊名為 Intel 7nm

Intel 3 估計是使用 7nm技術 , 舊名為 Intel 7+

Intel 20A 估計是使用 5nm技術 , 舊名為 Intel 5nm

Intel 18A 估計是使用 5nm技術 , 舊名為 Intel 5+