簡報時代背景:在1999年的10月6日,秋季微處理器論壇上演了計算機工業史上罕見的偉大一幕,藍色巨人IBM正式揭露了Power4處理器,其代號 “Regatta (兩艘並行的船隻)” 除了意指IBM當時在伺服器市場的兩大對手HP和Sun以外,更象徵著「原生雙核心」。「雙核惡魔」Power4的問世,不但一舉奠定了IBM未來站穩高階伺服器王者的地位,更是對HP/Intel IA-64指令集和Itanium處理器的正面回擊。筆者一直忘不了當時微處理器報導的副標題 “IBM Confronts IA-64, Says ISA Not Important (IBM面對IA-64,說指令集架構並不重要)”。

回顧消失在歷史洪流的Intel旗艦處理器Itanium(上)

回顧消失在歷史洪流的Intel旗艦處理器Itanium(中)

回顧消失在歷史洪流的Intel旗艦處理器Itanium(下)

硬科技:HotChips 32的新牙膏 IBM Power10與z15篇

如果各位科科難以第一時間感受到當時IBM Power4造成的震撼有多巨大,筆者就回顧一下當時其他廠商的狀況。

-

併購DEC的Compaq,在同一屆秋季微處理器論壇首次公開Alpha 21464 (EV8) 的同時多執行緒 (SMT) 架構。

-

AMD說「我們已經把Athlon的時脈拉到700MHz,好棒棒」,順便透露一部分「我們準備將x64指令集64位元化」的緣由和計畫。

-

Intel的Pentium III最高時脈還在733MHz,而Pentium 4上市則是一年後的事情。

結果IBM竟然在1999年底,不但完成了Power4的設計、推出了第一版樣品晶片、所有製程與封裝相關的參數也都鉅細靡遺的公諸於世,連包四顆Power4、總腳位多達5500隻的多晶片模組 (MCM) 都搬出來講了,也有實品照片,這是什麼妖術?一口氣把所有競爭對手甩的遠遠的。別說看不到車尾燈,根本就是被繞一圈了。雙核心?那是什麼?可以吃嗎?

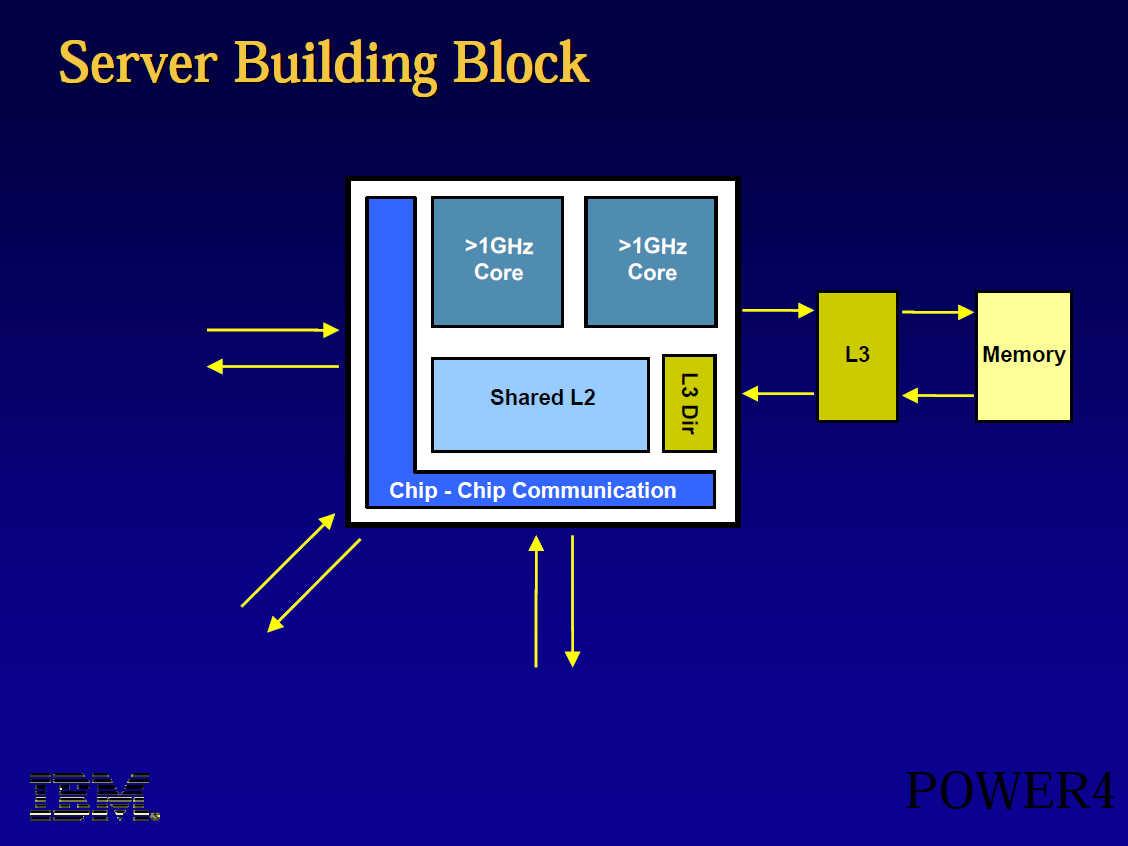

光從這個八核心多晶片模組的結構圖,就可以很清楚的看出,由內到外,Power4是一個不折不扣的頻寬怪物。

但Power4更可怕的是變態到極點的核心微架構:在1999年變出「8指令派發」的非循序指令執行 (那時x86的世界頂多就3個,多數RISC諸神大概也頂多4個)。

此外,IBM為了提高Power4的時脈,透過將五個解碼後微指令「打包」成類似超長指令集 (VLIW) 的指令包,垂直對應內部8個執行單元,然後要完全執行完畢後才能退返 (Retire),單一Power4核心僅同時處理20個指令包 (等同100個微指令),但這樣也大幅度的簡化控制單元的複雜度,讓Power4的時脈可從1.1GHz起跳。雖然當Power4在2001年初實際上市時 (越高階的產品往往需要更長的產品驗證期,況且IBM賣的是軟硬兼備的整台伺服器),1.3GHz的時脈看起來也沒那麼厲害了,但Power4就算時脈輸人,光靠內部的「寬度」就可以活活壓死競爭對手了。

至於Power4這種簡化後的非循序指令執行核心,可能造成內部執行單元利用率不足的疑慮,日後則由整合記憶體控制器並導入SMT的Power5所克服,在2004年的夏天上演了一連串的效能標竿大屠殺。

超大型多處理器架構本來就是IBM Power這種高階伺服器用處理器的拿手好戲,從系統匯流排、快取記憶體、快取資料一致性協定和高可用性,都遠非x86陣營所能企及,只要四個8核心模組,就能打造出32個核心的大型系統。

結合眾多的重大技術創新,微處理器報導在2000年2月7日,將年度最佳技術獎項 (Best New Technology) 頒給IBM Power4,打敗了Compaq Alpha 21464 (但還是得到了榮譽獎,只能說碰到誇張到極點的Power4真的很倒楣,畢竟人家都把東西做出來給大家看了)、Fujitsu/HAL SPARC64 V、被IBM視為「要盡快趕下海」的HP/Intel IA-64指令集架構、Sony/Toshiba的Emtion Engine/Graphics Synthesizer (Sony Playstation 2的兩顆主要晶片) 和Sun的MAJC。

用某部沒事亂改設定的畫不完漫畫「五星物語 (FSS)」當例子,IBM Power4的橫空出世,彷彿就像天照帝公開搭載雙光粒子引擎的雷德幻象,讓競爭對手們陷入恐慌的「雙核惡魔」。

不過時過境遷,靠著雲端資料中心的快速發展,讓Intel和AMD的高階x86處理器的競爭力,也遠非昔日吳下阿蒙 (起碼論成本優勢的確如此),以後應該也很難看到這樣的「奇蹟」了。隨著時代的演進,我們也失去了很多有趣的好東西,這也許是其中一件吧。

3 則回應