PA-RISC主要有3個發展里程碑:

-

1986年:1.0版。那時只有16個64位元浮點運算暫存器。

-

1991年:1.1版,基於效能考量,64位元浮點暫存器倍增到32個 (可視為64個32位元或16個128位元),追加MAX-1 (Multimedia Acceleration eXtensions) SIMD多媒體延伸,創此風氣之先,比其他高階RISC指令集都來得早。

-

1996年:2.0版,擴充成64位元,引進MAX-2和浮點累積乘加指令 (Fused Multiply-Add)。

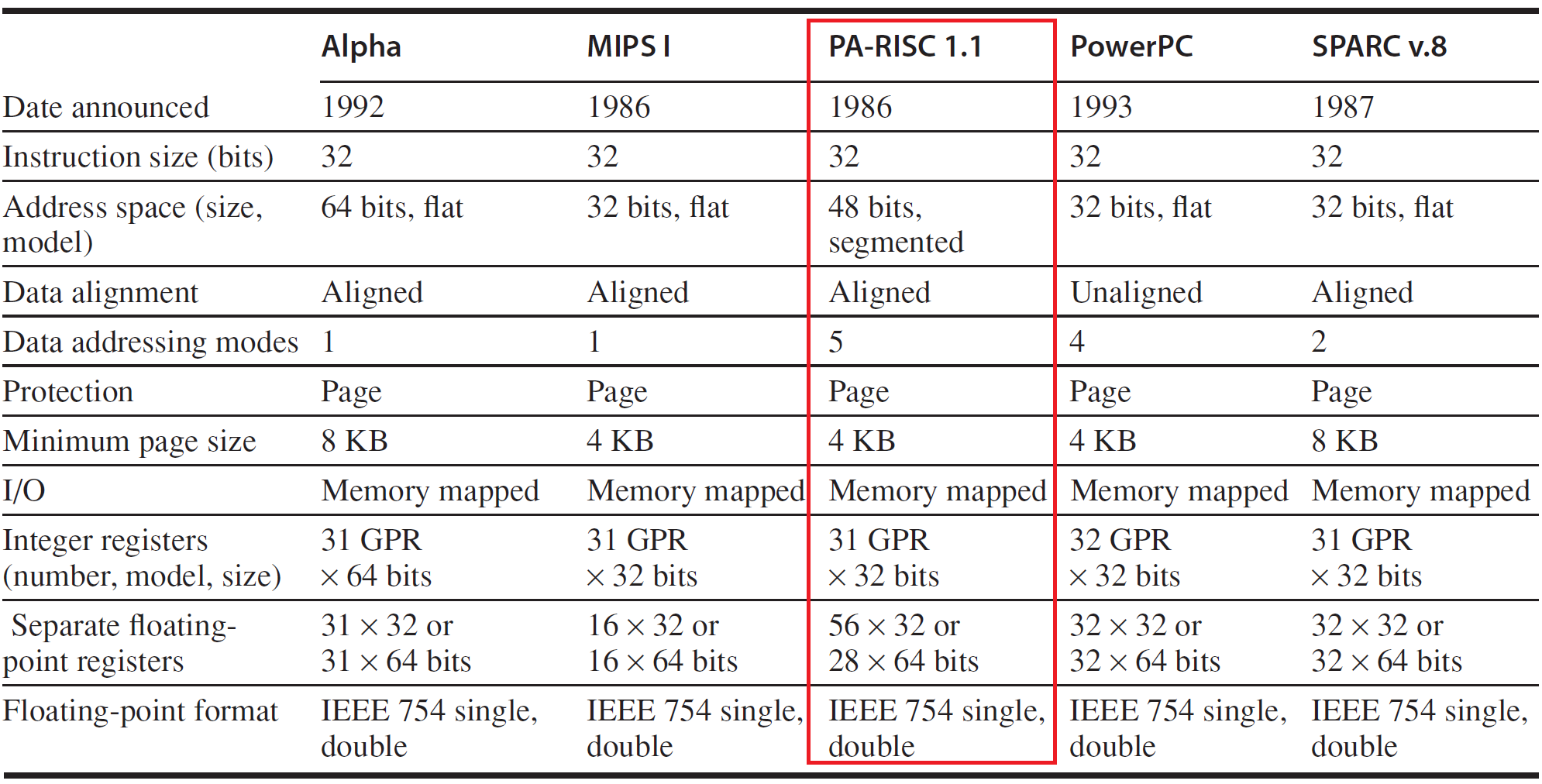

筆者在首篇有提到「PA-RISC是伺服器應用的RISC指令集中,最富CISC色彩者 (其實ARM在ARMv8 AArch64之前,因蘊含大量嵌入式應用的必備特色,也一直被戲稱是『CISC精神的RISC』)」,並非空穴來風,我們就先來看看當代最偉大的2位計算機結構大師 (David Patterson和John Hennessy) 是怎麼評論PA-RISC的:

“PA-RISC perhaps has the most unusual features of any desktop RISC machine. For example, it has the most addressing modes, instruction formats, and, as we shall see, several instructions that are really the combination of two simpler instructions.”

簡而言之,PA-RISC就是:

-

定址模式比同期的其他RISC還要多,然後連記憶體定址空間都還是古老的「節區 (Segmentation)」方式,而非平面 (Flat),Intel和AMD對此一定很有「感觸」。

-

1個複雜指令抵過2個簡單指令。

雖然HP設計PA-RISC指令集時,設定了目標「與微架構無關 (晶片設計師當然不希望吃飽閒閒沒事被指令集的詭異行為,為了維持精確中斷這樣的基本需求,硬逼著節外生枝變出奇怪的硬體)」,但很不幸的是,PA-RISC還是繼承了早期單一指令管線時期RISC的陋習:諸多延遲分支 (Delayed Branch)、延遲載入回存 (Delayed Load/Store)、和延遲中斷 (Delayed Interrupt) 這些在分支預測 (Branch Prediction)、深度超管線 (Superpipeline) 和超純量管線 (Superscalar) 時代根本只是一無是處的累贅,都需要追加額外的「運算結果作廢 (Nullification) 指令」與在微架構層面增加相對應的功能電路。

「先斬後奏」的「合併式 (Combined) 條件運算指令 (或稱為Guarded Execution和Conditional Execution)」也是PA-RISC引領指令集設計潮流的一大特色。指令在完成功能任務的同時,一併檢查是否符合條件,如果不符合就視同「無操作 (NOP)」,等於是用1個指令去做2個指令的工作。ARM自從v4後的全部指令都是這樣,x86的世界則是在Pentium Pro時加入了cmov (Conditional Move)系列。

但後來的歷史卻證明了,這看似簡潔優雅的設計,卻對實作大型化多指令派發微架構有著極度不利的負面影響 (等於要在擷取並解碼指令的時候,強行預先配置後方執行單元的資源)。原先整個指令系統都具備條件執行的ARM,在邁向64位元的歷史關鍵時刻,就義無反顧的徹底放棄了這沈重的包袱,連做為ARM最大潛在競爭對手的RISC-V,都沒有這類型的指令。

ARM在64位元世代可以頻頻冒出效能突飛猛進的微架構 (Apple就是最好的例證),這「斷、捨、離」絕對是最重要的關鍵因素,沒有之一。

最後,就是商業大型主機 (Mainframe) 的必備品:COBOL程式語言最需要的10進位數字處理,PA-RISC有五個指令可提供32位元到10進位數的轉換作業。下一個高階RISC處理器對於10進位數字有這麼巨大的「投資」,就筆者印象所及,就是2007年的IBM「超高時脈雙核惡魔」Power6了。

但以上只是PA-RISC「身為RISC中的CISC」的冰山一角,況且,更加精彩刺激的內容,還在下一期呢。(編輯部:你寫PA-RISC三連發騙稿費不夠還要再補一槍喔?)

4 則回應