前情提要:在經過1995-1998年的醞釀期之後,Intel Xeon伺服器用處理期也要進入P6微架構的草創期了!相較於五窮六絕的Pentium時期,怎麼說都是飛躍性的進步。

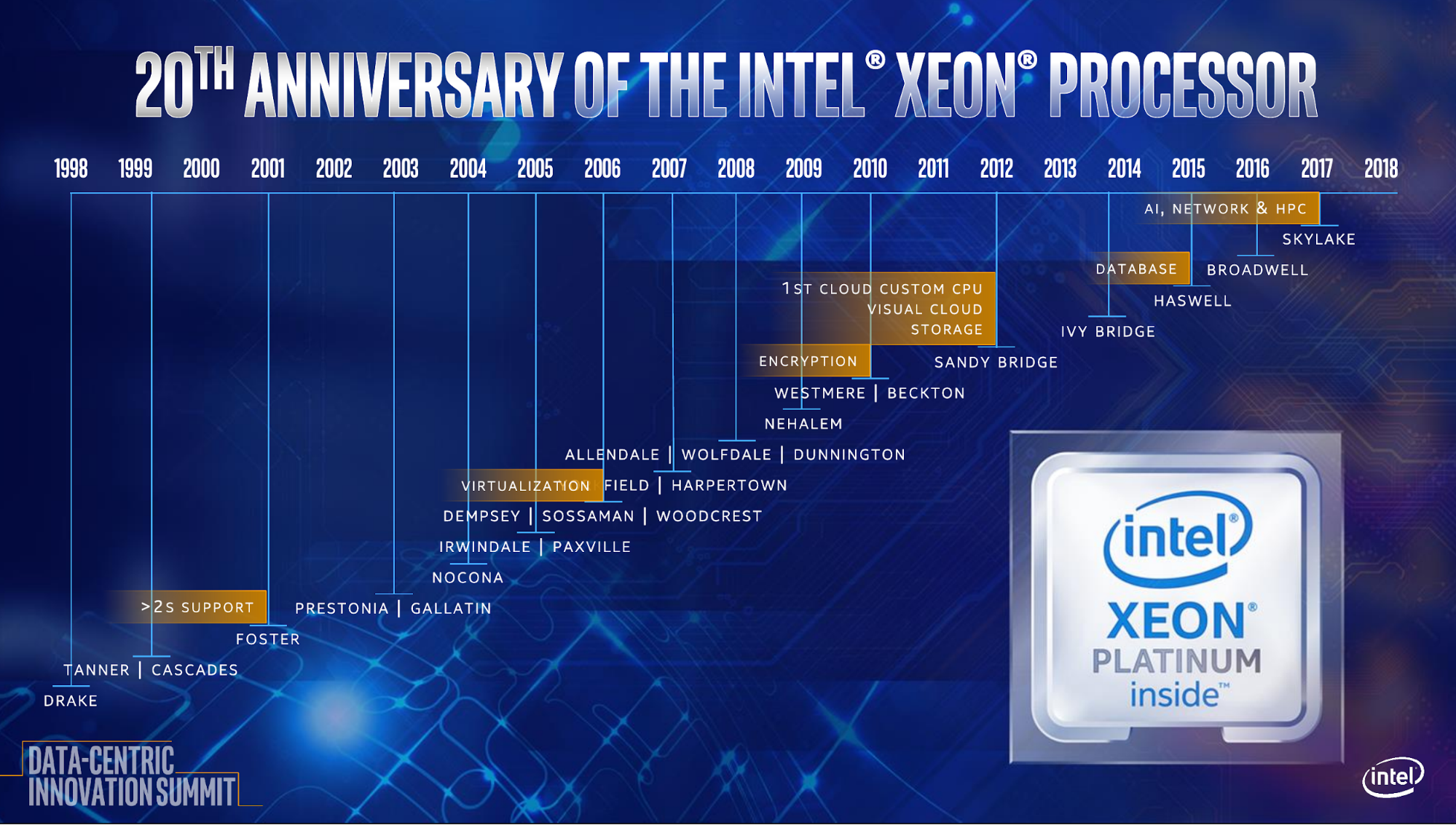

Intel的Xeon處理器發展史,基本上可分成以下時期。

- P6微架構問世後的「醞釀期(1995-1998)」。

- P6微架構的「草創期(1998-2001)」。

- 32位元單核NetBurst微架構的「擴張期(2001-2004)」。

- 64位元雙核NetBurst微架構的「混亂期(2004-2006)」。

- NetBurst轉向Core(Merom)的「轉換期(2006-2008)」。

- Nehalem徹底終結AMD技術優勢的「反擊期(2008-2011)」。

- 「x86義和團」與超級多核心Larrabee死灰復燃的「暴走期(2010-2018)」。

- 持續小步快跑,直到壓垮AMD的「鐘擺期(2011-2017)」。

- 堅守14nm製程的「牙膏期(2017-2020)」。

那從現在呢?大概就是「振作期(Since 2020)」了吧。

理所當然,我們就從草創期開始講起。萬丈高樓平地起,尚未洗乾淨「一身菜味」的Intel,首要之務莫過於推出「一看就知道跟個人電腦沒啥關聯」的產品,看起來頗有「高階產品感」的巨大Slot-2「彈夾」就為此而生。

但Intel並非只為了讓Xeon看起來比較專業,才搞出這樣的巨大塑膠盒,更為了因應更高容量的同核心時脈L2快取記憶體。原先242隻針腳的Slot-1無法滿足其供電需求,擴展為330隻的Slot-2,趁機塞入系統管理匯流排(SMBus),並將原生的多處理器支援性,恢復到Pentium Pro的4顆(Pentium II僅2顆)。此外,為確保四處理器時,系統匯流排(俗稱的「外頻」)可跑到100MHz,在Intel擁有專利的GTL+之外,進一步引進AGTL+訊號準位,在Pentium III世代提升到133MHz。

P6時期的多處理器環境大致上就長這個樣子,相較於五窮六絕的Pentium時期,怎麼說都是飛躍性的進步。

記憶體容量和快取記憶體的定址範圍也是另一個重頭戲。為了突破32位元的4GB限制,除了Pentium Pro問世的PAE-36模式,Pentium II世代Xeon(代號Drake)追加「效能較低,但作業系統比較不需要大興土木」的PSE-36。此外,Pentium II世代Xeon的L2快取記憶體可涵蓋到整個64GB可定址記憶體範圍,不像早期的Pentium II有著512MB或4GB的限制(這對採用Pentium II組裝伺服器造成不小的麻煩),提高資料可靠度的ECC糾錯,更是必備的制式武裝。

說到快取記憶體「看得到卻吃不到主記憶體」這件事,早在Pentium時代就發生過了。以430HX晶片組為例,如果不額外安裝Tag RAM,主機板上的L2快取就只摸得到前64MB。

話說回來,CPU可定址這麼大的記憶體容量是一回事,如果系統晶片組沒辦法吃的下來也是白搭。當時最高階的450NX也才8GB,後來Intel併購Corollary公司,得到其Profusion PCIset晶片組(8處理器,原先對應Pentium Pro),如此高檔的貨色,也只能裝到32GB。

如同低價電腦的Celeron,Pentiun III時代後期的Xeon,隨著製程技術的進步,逐步將L2快取「吸回」CPU本體,實乃大勢所趨。在2001年3月21日登場的Xeon 900A(代號Cascades 2M),內建多達2MB的L2快取,開Intel實作大型化快取記憶體之先河。

也難怪日後Intel常被這樣開玩笑:這間公司最大的業務不是CPU,而是快取記憶體。真是太讓人感到科科了。