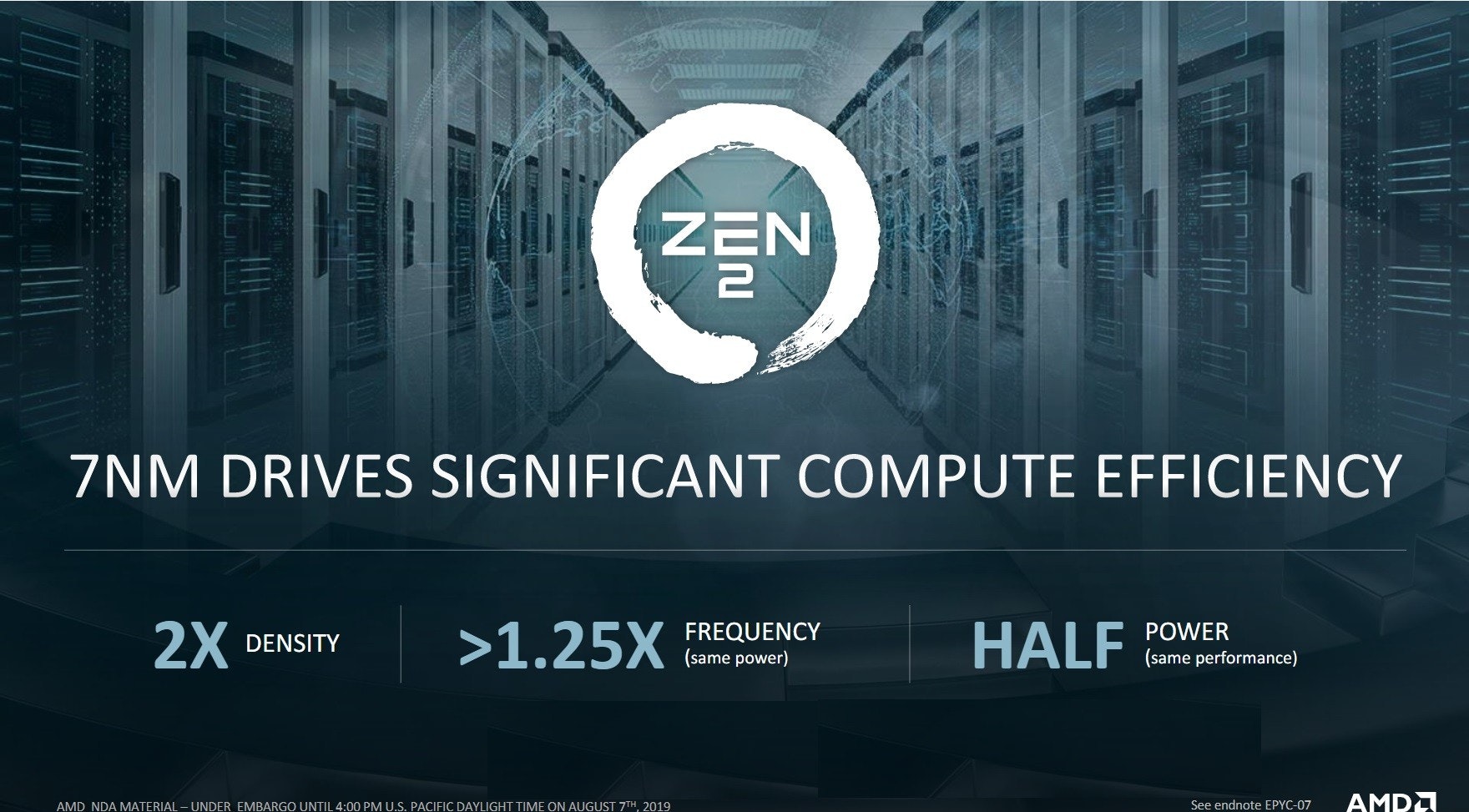

AMD 稍早正式宣布第二世代 EPYC 平台、代號 ROME 的伺服器處理器發表,也是繼 2017 年推出第一代 EPYC 平台後一次全新的大升級,此次將核心架構提升到新世代 7nm 的 Zen 2 ,並且以獨特的 9 DIE 異構封裝系統級單晶片,在最大核心數量、記憶體支援與 I/O 頻寬等大幅提升,也是 AMD 寄予厚望能在伺服器挑戰 Intel Xeon 霸業的新一代平台。

▲ AMD 強調第二世代 EPYC 全產品線特色功能皆相同

▲ EPYC 7002 系列名稱後帶有 P 的為單插槽平台用產品

▲ AMD 強調不因產品定位讓中低階產品在 PCIe 總線、記憶體通道也閹割

▲單插槽產品線藉由減少快取降低成本

相較代號 7001 系列的第一代 EPYC ,代號 7002 系列的 EPYC 自最低 8 核心到最高 64 核心提供豐富的產品項目,同時全系列都是採用均一的 Zen 2 架構,在技術上具備一致性,特別強調不會像競爭對手在不同級別的產品就對記憶體通道、 PCIe 總線等有所增減。不過 AMD 為了使產品價格更為實惠,特別針對單插槽伺服器規劃產品線,藉由較小的快取使價格比起針對雙插槽設計的產品線更便宜。

▲ 第二代 EPYC 由原本單一晶片 4 CPU DIE 進化為 8 CPU + 1 I/O DIE 的混合架構封裝

▲藉由 Infinity Fabric 與將工作分配管理集中到 I/O DIE ,使得第二代 EPYC 延遲更低、多核溝通更快

▲ BOOST 的時脈可依照工作負載情況調整,藉此維持能耗、發熱與性能的平衡

代號 EPYC 7002 系列的第二代 EPYC 處理器最大的特色就是進一步將第一世代的 Multi-Die SIP ( System in a Package ) 設計發揚光大,此次將 I/O 也一併整合到 SIP 的封裝上,利用基於 Infinity Fabric 的 14nm I/O DIE 管控 8 個基於 7nm Zen 2 架構的最高 8 核心 CPU DIE ,並輔以較前一世代更多的 DDR RAM 快取,大幅提升多核心協作的相互溝通能力與相互存取。同時,全新的能源管理機制能使第二代 EPYC 依照當前運算負載的不同動態調節核心的 Boost 情形,並兼顧能耗、發熱與效能。

▲不同於前一世代繁瑣的多核溝通方式,採用 I/O DIE 統一管理 CPU 與快取的第二代 EPYC 大幅降低多核心與跨處理器溝通延遲

且 EPYC 7002 系列也改善雙處理器平台之間相互溝通的流程,藉由處理器的 CPU DIE 與快取管理方式集中化,使得一個 CPU SoC 就是一個 NUMA ,相較上一代的雙 CPU 平台需要將每個 CPU DIE 視為單一 NUMA 、等同雙 CPU 共 8 個 NUMA 的情況,第二代 EPYC 直接進行每個 CPU DIE 的工作分配,不再需要由其中一個 CPU DIE 發號司令分配工作到其它三個 DIE ,同時搭配傳輸速率更高的 Infinity Fabric 取代前一代 DIE 與 DIE 連接的 PCIe ,大大降低多核溝通與跨處理器溝通的延遲。

▲ EPYC 具備獨立的硬體級安全核心

▲ AMD 特別強調高度安全性、尤其是沒有競品當前面臨的 Meltdown 漏洞

▲ EPYC 強調具備高度安全性的記憶體加密

▲藉支援 SME 避免被進行物理性的記憶體攻擊

▲強調虛擬化也具備高度安全性

▲第二代 EPYC 可藉由 SEV HOST+ 提供最多 509 個使用者的虛擬化

安全性對於伺服器、資料中心是相當重要的, AMD 也不忘在 EPYC 強調其安全設計, AMD 在架構中整合獨立的硬體級安全核心,基於 Arm 的 Cortex-A5 ,藉此為處理器的安全與企業虛擬化等把關,除了基本的企業與虛擬化安全性,更指出不受如 Meltdown 等微架構設計層面的硬體漏洞影響。同時, AMD 更強調第二代 EPYC 平台的記憶體加密技術,無論是針對物理性攻擊防護或是虛擬化的記憶體安全,都提供多層面的安全加密技術,同時相較第一代 EPYC 僅能提供 15 個 memory key ,第二代 EPYC 提供達 509 個 memory key 可在高度安全的 SEV HOST+ 下提供最多 509 個用戶的虛擬化服務。

▲雖 EPYC 維持與前一代相同的 8 通道記憶體支援,但由於支援最高時脈提升到 3200MHz ,亦具備更高的記憶體頻寬

▲ PCIe 4.0 有助提升如儲存、介面卡與網路的傳輸速度

記憶體與 I/O 通道也是 AMD 第二代 EPYC 的重要特色,雖然考量 CPU 快取維持與第一代 EPYC 相同的 8 通道記憶體,不過可支援最高 3200MHz DDR 4 ,也進一步提升記憶體通道頻寬,並最高提供單一處理器 4TB RAM 的總記憶體;此外第二代 EPYC 也是 PCIe 4.0 Ready 的處理器,單一處理器能夠提供 128 條 PCIe 4.0 總線、共 512GBps 傳輸性能(雙插槽最多提供 162 條總線), 128 條總線可分配成最多 8 條 PCIe 4.0 x 16 ,對於儲存或是擴充高速互聯網路卡等,皆能夠帶來較 PCIe 3.0 更好的傳輸性能與更低的延遲。

▲ AMD 強調 EPYC 是以新一代資料中心、超算應用逐步進化的處理器

對比第一世代 EPYC ,第二世代的 EPYC 在兩年的時間自基礎架構設計到封裝技術等都有顯著的變化,但同樣以同價位最高性能表現作為訴求,而第二世代的 EPYC 以創新的混合架構封裝系統級單晶片與加大快取設計方式,大幅降低多核心協作的延遲,輔以 8 通道 DDR4 3200MHz 記憶體支援、 PCIe 4.0 等創新技術,以及最高單 CPU 64 核心的設計,希望能在資料中心領域重新站穩腳步,而在活動上多家系統廠商、雲端服務商站台助陣的情況,也顯示 AMD 第二世代 EPYC 的設計規劃正確命中市場需求,然而 AMD 能否結合握有的 Radeon GPU 技術,強化自身平台異構運算的表現,或許也是 AMD 在 CPU 穩定之後下一步的重要戰略。