閱讀本文之前,請先參閱前情提要「為悼念Intel NetBurst的失敗而刻下的墓誌銘 (上)」、「為悼念Intel NetBurst的失敗而刻下的墓誌銘 (中)」。回到主題,Netbust雖然在初代Pentium 4 “Willamette” 剛推出時,因初期產品的部分效能,還不如更低時脈的Pentium III,而飽受批評,但邁入130nm製程的Northwood世代,卻轉危為安,頗受好評。那麼,「身中三十多刀,還被認定自殺」的NetBurst是如何失敗的?其真實死因,眾多紛紜,但歷史的教訓已經證明,史詩級的慘劇,永遠都是天時、地利、加上人和的結晶。

- 天時:Intel被微軟力挺的AMD x86-64搞的不要不要的。

- 地利:Intel首次大規模導入自動化佈線,偏偏Prescott又需趕鴨子上架。

- 人和:Intel內部的策略失當與管理問題,讓Tejas專案完全失控。

問題的根源很單純:讓Intel進退失據的Itanium。

Intel原本欽定IA-64是「僅此一家別無分號」的64位元指令集架構,但預定1998年就該上市的Itanium,產品時程一再延宕,上演Intel操刀的第一代產品、和舊HP團隊負責的第二代產品、上市時間相隔不到一年的荒謬劇場,全新指令集架構缺乏足夠軟體資源,而原生軟體的執行效能也缺乏競爭力,加上其相容x86的硬體解決方案,吃力不討好,效能慢到一點實用性都沒有,種種因素累積下來,導致Itanium沒有獲得如Intel樂觀預期的成功。

更糟糕的是,AMD靠著享有微軟支持、又兼顧x86相容性的x86-64,一路步步進逼。

微軟擺明力挺AMD的64位元x86規格 (雖然他們抱持著挑戰IBM的夢想,支持Itanium好一段時日,但最終仍不得不抽腿),也拒絕Intel自己原本代號Yamhill的64位元x86指令集擴充方案,讓一心推動IA-64的Intel從此陣腳大亂,內部也爆發路線之爭,埋下了迫使幾位涉足伺服器相關事業單位的高階主管,其中亦不乏有力爭奪Intel執行長大位者,像跳槽Cadence的Mike Fister和現任VMware執行長的Pat Gelsinger,日後紛紛求去的種子。

微處理器業界極具權威性的微處理器報導(Microprocessor Report),在2004年2月5日公布2003年度分析師精選獎項(Annual Analyst’s Choice Award)中,Prescott核心的Pentium 4(加上AMD Athlon 64 FX-51)被同樣90nm製程的IBM PowerPC 970FX擊敗,痛失最佳桌上型處理器的獎項。在評鑑中,微處理器報導對Prescott作出以下的評論:

「經過兩年的承諾、暗示和謠言後,結果令人有些失望。為何Intel要如此大費周章發展Prescott?就我們所知的事實,如果只為了要在2004年底前,實現4GHz的承諾,這個計畫似乎還是不值得它所耗費的成本。就算沿用Northwood核心,只要採用90nm製程以及更大容量的快取記憶體,我們相信也可以得到比Prescott更小、更快的處理器。」

也如我們所目睹的,陣腳大亂的Intel,急急忙忙的在90nm製程NetBurst「Prescott」導入與AMD相容的IA-32e (Clackamas Technology),而不是穩紮穩打的持續微縮已經很成功、Intel不願意公開承認還有很大時脈成長空間的130nm製程Northwood,況且在Intel的製程發展史上,兼備預應變矽晶圓 (Strained Silicon) 與低介電質佈線絕緣層 (Low-K Inter Layer)、代號P1262的90nm製程,是Intel有史以來良率改進速度最快者。

當時的「專業科技媒體」不乏「有識之士」指摘Prescott的問題只有「製程不好」,但他們絕對無法自圓其說:為何採用相同製程的Pentium M「Dothan」,就沒有一同共襄盛舉的引爆功耗失控的地雷。

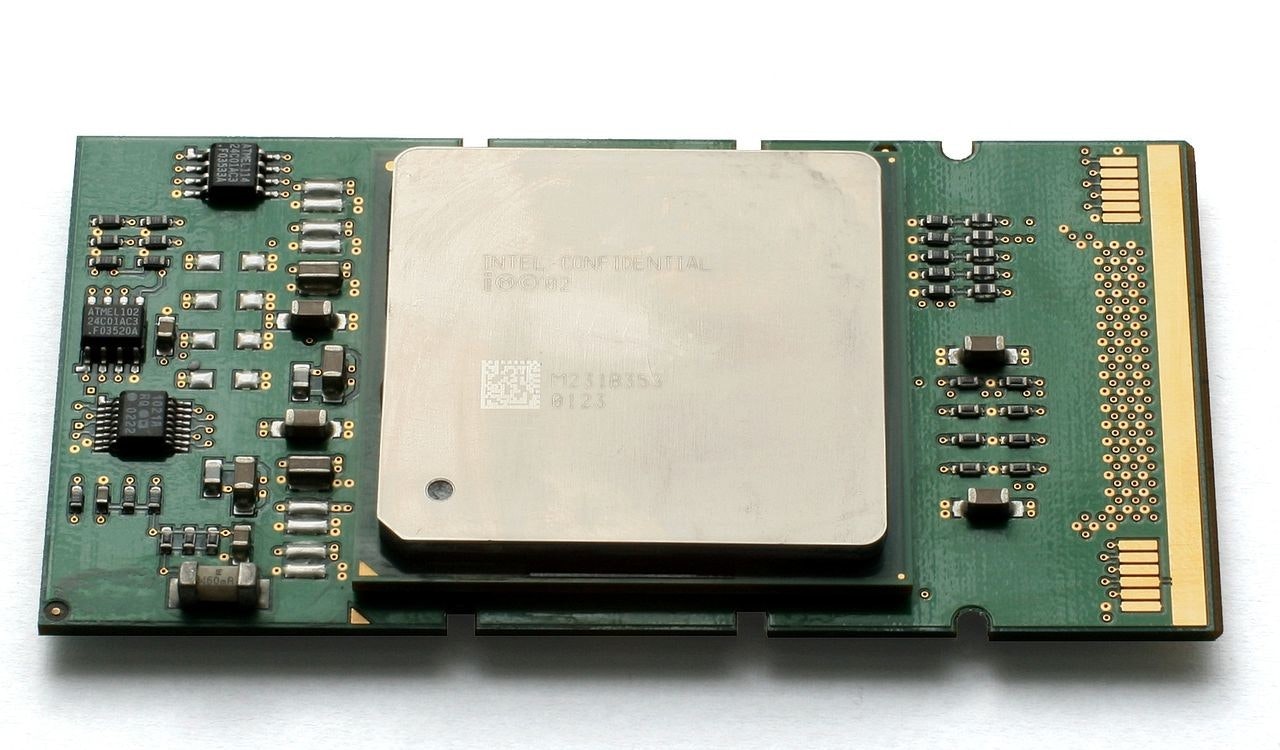

除了64位元,Intel在Prescott放入了虛擬化「Vanderpool」、安全運算「La Grande」、分頁表防禦緩衝區溢位攻擊的XD(Execution Bit)位元,與琳瑯滿目的電源管理(TM2、EIST、DBS、C1E)等,偏偏指令管線深度延長50%的Prescott,又是Intel史上第一次大規模引進自動化佈線的處理器,比例超過45%,而大幅度擴張 (原先只有高速ALU和AGU,變成所有整數邏輯運算包含第一階資料快取) 的2倍時脈功能單元,從不到100萬電晶體激增到680萬,Wave Pipeline又物極必反的帶來塞好塞滿的訊號緩衝器,結果不只功耗失控,NetBurst最引以為傲的2大特色:0.5時脈週期的整數指令輸出率,與超低延遲的資料快取記憶體,在急就章又不成熟的Prescott,通通都消失了。

最後,系出同源、相同製程、一樣單核、晶片面積卻「要五毛,給一塊」倍增的Tejas,竟然還可以生米煮成熟飯、進入成品出廠驗證 (Tape Out) 階段,甚至連datasheet都寫好、還印好出版,這就徹頭徹尾是Intel內部的管理問題了。裝滿外掛的Tejas究竟有多瘋狂?光從驚世駭俗的指令管線,和莫名其妙多出來的第二個指令解碼器,就可略見一斑,尤其後者根本就否定了NetBurst的初衷,難道Trace Cache不就是要用SRAM去交換昂貴的指令解碼器嗎?

然後NetBurst就這樣死掉了。

但塞翁失馬,焉知非福,失敗為成功之母,NetBurst的諸多設計規劃,日後都在Intel後繼的x86微架構陸續復活,Sandy Bridge就是融合成熟化的微指令快取,與引進分離式實體暫存器檔案型態、非循序指令執行引擎的技術結晶,也替輝煌的P6劃下完美的句點。

回到首篇文章的原點,時過境遷,暮然回首,NetBurst依舊是計算機工業史上極度罕見的話題性微架構,再多的千言萬語,亦述說不盡,就以當年某位友人的評論,作為本文的總結。

「一想到這麼莫名其妙的微架構,被製造成數億顆賣到市場上的產品,難道不覺得這很酷嗎?更厲害的是,這家公司竟然還沒倒耶!如果哪天Intel又三太子上身想重施故技,新架構該不會取名成WirelessBurst吧?」

絕對不會,應該不會,也許不會,希望不會,科科。